Сколько контактов на ddr2: Как узнать сколько контактов DDR2 на моей материнской плате ,если когда на планке оперативной памяти,которую я куплю.Форм-фактор FB-DIMM 240-контактн?

Содержание

Частые вопросы — Оперативная память

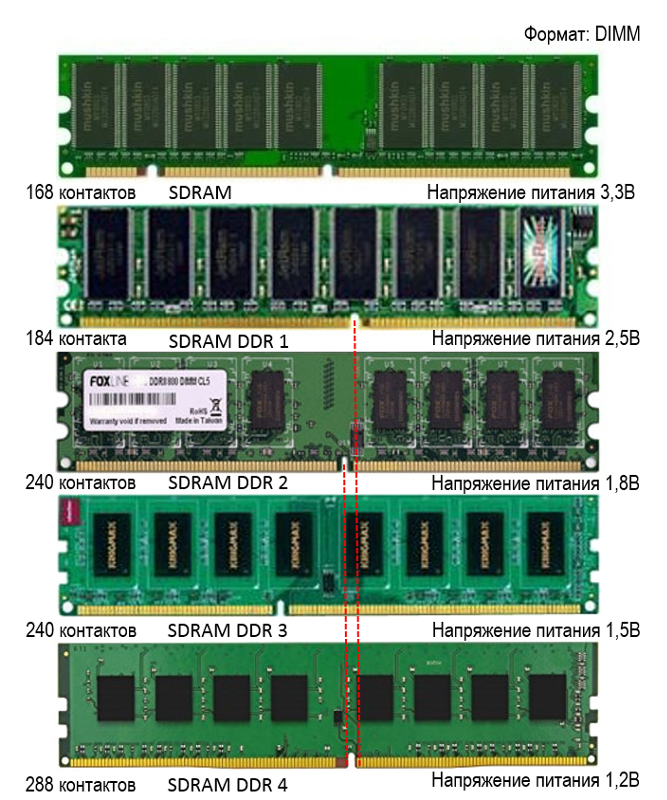

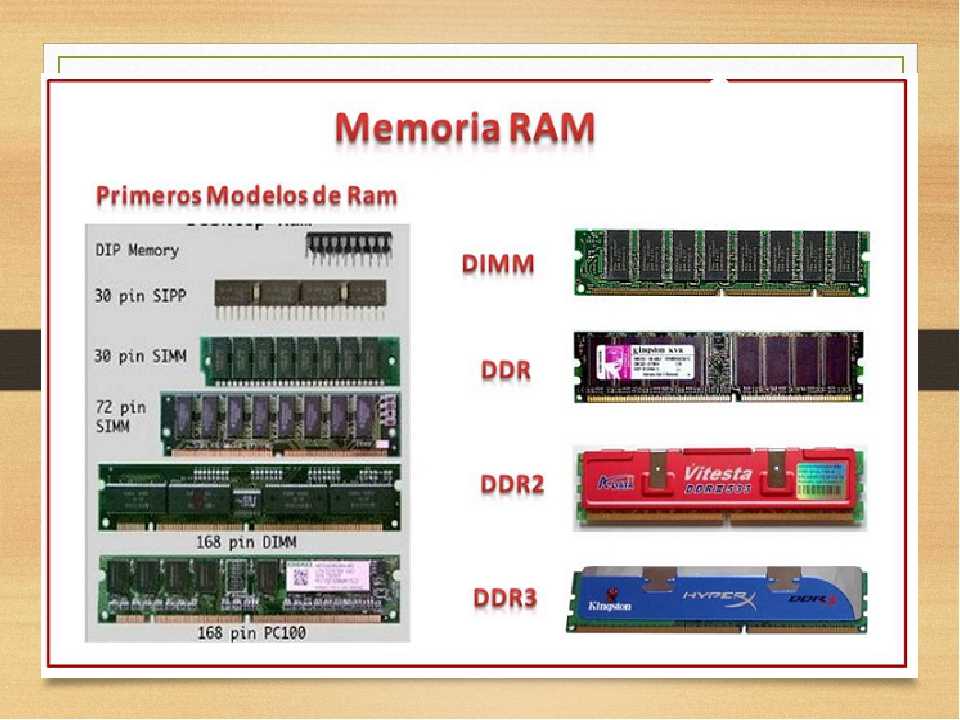

Форм-фактором называется стандарт, который определяет основные показатели модуля памяти (габариты, число и принцип расположения контактов). На рынке существует следующий ряд форм-факторов памяти, они физически несовместимы между собой:

- SIMM;

- DIMM;

- FB-DIMM;

- SODIMM;

- MicroDIMM;

- RIMM.

Рассмотрим их подробнее:

SIMM (Single in Line Memory Module). Модули форм-фактора SIMM бывают двух версий: 30-контактные и 72-контактные. Каждый контакт обладает выходом на обе стороны платы.

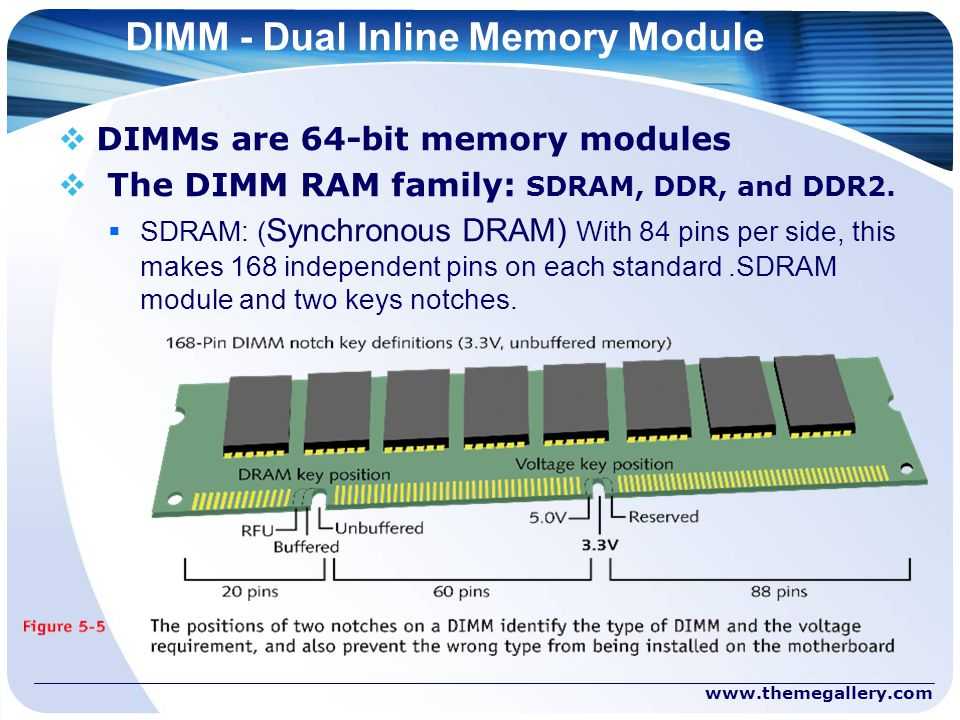

DIMM (Dual in Line Memory Module). Модули форм-фактора DIMM, обычно, бывают следующих типов: 168-контактные, 184-контактные, 200-контактные и 240-контактные. Независимые контактные площадки располагаются по обе стороны платы.

Независимые контактные площадки располагаются по обе стороны платы.

FB-DIMM. Данный стандарт модулей памяти используется в серверах. В механическом плане, этот тип модуля идентичен модулям памяти DIMM 240-pin, но при этом категорически несовместим с обычными небуферизованными модулями DDR2 DIMM и DDR2 DIMM (Registered).

SO-DIMM (Small Outline Dual In-Line Memory Module). Уменьшенная вариация стандарта DIMM. Применяется, в основном, в ноутбуках и устройствах типа Tablet PC. Распространенные модули форм-фактора SO-DIMM — 144-контактные и 200-контактные. Реже встречаются 72- и 168-контактные.

MicroDIMM (Micro Dual In-Line Memory Module). Еще более уменьшенная в габаритах, по сравнению с SO-DIMM, версия DIMM. В основном, данный форм-фактор устанавливается в субноутбуки. Оснащается 60-контактной площадкой. На рынке существуют следующие варианты MicroDIMM: 144-контактный SDRAM, 172-контактный DDR и 214-контактный DDR2.

RIMM. Данный форм-фактор распространяется на все модули памяти типа RIMM (RDRAM). На рынке существуют следующие вариации данного форм-фактора: 184-контактная, 168-контактная и 242-контактная.

Важно: при выборе форм-фактора модуля оперативной памяти, необходимо иметь ввиду, что материнская плата, на которую в дальнейшем будет устанавливаться данная память, должна иметь поддержку выбранного форм-фактора оперативной памяти.

Тип — очень важный параметр оперативной памяти. Им определяется ее внутренняя структура и основные характеристики. В настоящее время, на рынке существуют 5 основных типов оперативной памяти:

- SDRAM;

- DDR SDRAM;

- DDR2 SDRAM;

- DDR3 SDRAM;

- RIMM.

Рассмотрим подробнее каждый из них:

SDRAM (Synchronous Dynamic Random Access Memory) — синхронная динамическая память, обладающая произвольным доступом. В отличие от типов памяти предыдущих поколений, обладает функцией синхронизации с системным генератором. Это дает возможность контроллеру памяти точно определять время готовности данных, что существенно сокращает временные задержки, возникающие в процессе циклов. В недалеком прошлом, данный тип оперативной памяти широко применялся в ПК, однако сегодня тотально вытеснен с рынка типом DDR и его «последователями».

В отличие от типов памяти предыдущих поколений, обладает функцией синхронизации с системным генератором. Это дает возможность контроллеру памяти точно определять время готовности данных, что существенно сокращает временные задержки, возникающие в процессе циклов. В недалеком прошлом, данный тип оперативной памяти широко применялся в ПК, однако сегодня тотально вытеснен с рынка типом DDR и его «последователями».

DDR SDRAM (Double Data Rate SDRAM) — синхронная динамическая память, обладающая случайным доступом и удвоенной скоростью передачи. Ключевым преимуществом типа памяти DDR SDRAM перед типом SDRAM является увеличенная вдвое пропускная способность памяти, при той же тактовой частоте. Так, за один такт системного генератора производится не одна, как в SDRAM, а сразу две операции с данными. Отсюда и название: Double Data Rate (удвоенная скорость передачи данных).

DDR2 SDRAM — следующее поколение памяти DDR, второе по счету. Являясь эволюционным продолжением DDR, новое поколение сохранило в себе принципы функционирования «предшественника». Ключевое отличие кроется лишь в том, что в новом типе производится выборка 4-х бит данных за один такт, тогда как в первом DDR осуществлялась 2-х битная выборка. Кроме того, DDR2 отличается более низким энергопотреблением, меньшим тепловыделением и большей рабочей частотой.

Являясь эволюционным продолжением DDR, новое поколение сохранило в себе принципы функционирования «предшественника». Ключевое отличие кроется лишь в том, что в новом типе производится выборка 4-х бит данных за один такт, тогда как в первом DDR осуществлялась 2-х битная выборка. Кроме того, DDR2 отличается более низким энергопотреблением, меньшим тепловыделением и большей рабочей частотой.

DDR3 SDRAM — следующее за DDR2 SDRAM поколение оперативной памяти. В нем применяется та же технология «удвоения частоты», что и в DDR2. Ключевыми отличиями нового поколения памяти от предшествующего являются: возможность работы на более высокой частоте, и меньшее энергопотребление. Модули памяти DDR3 оснащены специальными «ключами», представляющими собой ориентирующие вырезы. Эти вырезы имеют явные отличия от «ключей» модулей памяти DDR2. Так, модули DDR3 и DDR2 не имеют совместимости со старыми слотами.

RIMM (RDRAM, Rambus DRAM) — синхронная динамическая память. Автором и разработчиком данного стандарта является корпорация Rambus. Главное отличие типа RIMM от DDR-памяти заключается в увеличенной тактовой частоте, которую удалось добиться благодаря сокращению разрядности шины при одновременной передаче номера строки/столбца ячейки в ходе обращения к памяти. Обладая чуть более высокой производительностью, RDRAM, при выходе на рынок, была значительно дороже DDR. Это повлекло за собой практически тотальное вытеснение RIMM с рынка оперативной памяти.

Автором и разработчиком данного стандарта является корпорация Rambus. Главное отличие типа RIMM от DDR-памяти заключается в увеличенной тактовой частоте, которую удалось добиться благодаря сокращению разрядности шины при одновременной передаче номера строки/столбца ячейки в ходе обращения к памяти. Обладая чуть более высокой производительностью, RDRAM, при выходе на рынок, была значительно дороже DDR. Это повлекло за собой практически тотальное вытеснение RIMM с рынка оперативной памяти.

Выбирая оперативную память, пользователь, прежде всего, должен ориентироваться на возможности имеющейся/выбранной материнской платы, поскольку в параметрах «материнки» заложена совместимость с тем или иным модулем памяти.

Это определенный характер расположения чипов на модуле памяти. Модули могут быть как с односторонней, так и с двусторонней упаковкой. Когда микросхемы установлены с обеих сторон модуля, толщина модуля, соответственно, увеличивается. Физически, такие модули не могут устанавливаться в некоторые системы.

Физически, такие модули не могут устанавливаться в некоторые системы.

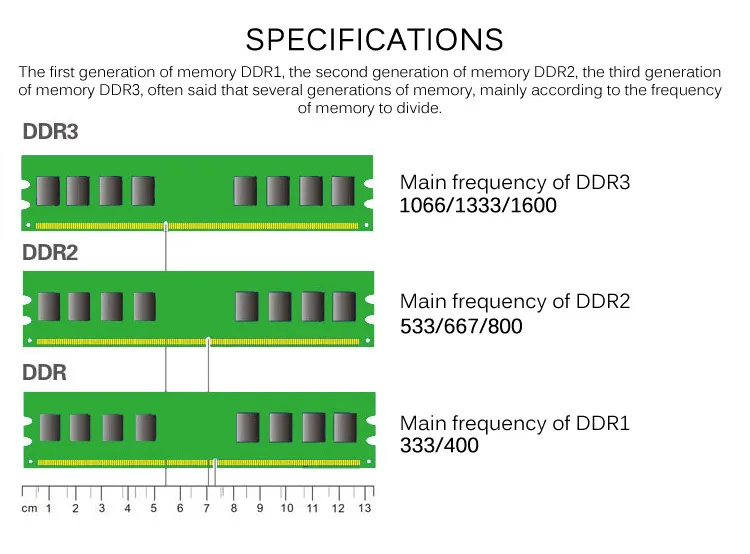

Тактовая частота — это максимальная частота системного генератора, на которой синхронизируются процессы приема/передачи информации.

В типе памяти DDR (а также DDR2 и DDR3) указывается двойное значение тактовой частоты. Это делается потому, что за один такт осуществляется две операции с данными.

Чем выше тактовая частота, тем большее количество операций производится за единицу времени. Это дает возможность приложениям достигнуть более стабильной и быстрой работы. При прочих равных параметрах, память с более высокой тактовой частотой обладает более высокой стоимостью.

Некоторые модули памяти предназначаются исключительно для определенных ПК и ноутбуков. Это — специальные модули, выпускаемые производителями строго для определенных моделей. Однако, существуют и модули широкого применения, которые доступны для установки на различного рода компьютеры.

Это специальные металлические пластины, установленные на микросхемах памяти. Основной их функцией является улучшение теплоотдачи системы. Обычно, радиаторы устанавливаются непосредственно на модули. Однако, монтировать их имеет смысл только на высокочастотные модули памяти.

ECC (Error Checking and Correction) — алгоритм, способный обнаруживать и исправлять случайные ошибки, возникшие в результате передачи данных в системе оперативной памяти. Ошибка не должна превышать 1 бит в байте.

Ошибка не должна превышать 1 бит в байте.

Некоторые материнские платы рабочих станций имеют поддержку технологии ECC. Также, ею обладают почти все без исключения серверные платы.

Модули памяти с технологией ECC отличаются более высокой стоимостью, в сравнении с обычными модулями.

Рассчитать общий объем памяти можно, сложив объемы установленных в систему модулей памяти.

Обычному офисному компьютеру для работы в Интернете и простых приложениях хватит 512 Мб. Для комфортной работы с графическими приложениями потребуется 1 Гб (1024 Мб) памяти. Сложные графические программы, а также «тяжелые» компьютерные игры будут должным образом функционировать при 2 Гб (2048 Мб) памяти и выше.

Диапазон объема памяти одного модуля: от 0.03125 до 32.0 Гб.

Модуль памяти уменьшенной (по сравнению с габаритами стандартного модуля) высоты. Как правило, устанавливается в серверные корпуса с заниженным профилем (Low Profile).

Как правило, устанавливается в серверные корпуса с заниженным профилем (Low Profile).

Каждый модуль оперативной памяти рассчитан на определенный показатель напряжения питания. Вот почему при выборе модуля памяти важно проверить поддержку вашей материнской платой требуемого напряжения питания.

На одном модуле памяти может располагаться определенное количество чипов. Микросхемы этих чипов могут быть установлены как с одной, так и с обеих сторон платы модуля.

Диапазон количества чипов каждого модуля памяти: от 1 до 72.

Ранк — это область памяти, создаваемая чипами ее модуля. Обладает шириной 64 бита (72 бита, при наличии поддержки ECC).

В зависимости от конструкции, в модуле может быть расположено 1, 2 или 4 ранка.

В настоящее время, все серверные материнские платы обладают ограничением на суммарное количество ранков памяти. К примеру, если в материнской плате может быть установлено максимум 8 ранков или 4 двухранковых модуля, то свободные слоты не будут поддерживать дополнительные модули, поскольку это приведет к превышению установленного ограничения. Вот почему цена одноранковых модулей выше, в сравнении с 2-х- и 4-ранковыми.

К примеру, если в материнской плате может быть установлено максимум 8 ранков или 4 двухранковых модуля, то свободные слоты не будут поддерживать дополнительные модули, поскольку это приведет к превышению установленного ограничения. Вот почему цена одноранковых модулей выше, в сравнении с 2-х- и 4-ранковыми.

Модули памяти могут продаваться в наборе. На рынке, помимо одиночных планок, нередко встречаются комплекты по 2, 4, 6, 8 модулей памяти, обладающих идентичными характеристиками. Эти комплекты специально подобраны для работы в двухканальном режиме.

Применение двухканального режима значительно увеличивает пропускную способность оперативной памяти. Таким образом, увеличивается и скорость работы запущенных приложений. Тем пользователям, которым необходима высокая скорость работы игровых и графических приложений, следует обратить особое внимание именно на такие наборы модулей памяти.

При покупке отдельных модулей памяти, важно помнить, что модули даже с идентичными характеристиками, от одного производителя, но приобретенные по отдельности, могут не сработать в паре. При этом необходимо учитывать, что сама материнская плата должна иметь поддержку двухканального режима работы памяти.

При этом необходимо учитывать, что сама материнская плата должна иметь поддержку двухканального режима работы памяти.

Каждый модуль памяти обладает своим количеством расположенных на нем контактных площадок. Число контактов, находящихся в слоте оперативной памяти материнской платы, обязано совпадать с числом контактов на модуле.

Помимо идентичного количества контактов, совпадать должны и вырезы (ключи, препятствующие некорректной установке).

Диапазон количества контактов модуля памяти: от 144 до 244.

Модуль памяти может оснащаться специальными буферами (регистрами). Эти буферы довольно-таки быстро производят сохранение поступивших в них данных, а также сокращают нагрузку на систему синхронизации, давая дополнительное свободное пространство контроллеру памяти.

Установленный между контроллером и чипами памяти буфер образует дополнительную задержку в ходе выполнения операций. Эта задержка составляет обычно 1 такт. Так, показателя высокой надежности можно добиться лишь путем сокращения (пускай и незначительного) быстродействия памяти.

Эта задержка составляет обычно 1 такт. Так, показателя высокой надежности можно добиться лишь путем сокращения (пускай и незначительного) быстродействия памяти.

Буферизированные модули памяти отличаются весьма высокой стоимостью и применяются в основном в серверах. Следует также отметить, что буферизованная и небуферизованная память не имеет между собой совместимости.

tRP — это количество тактов между командой закрытия строки и командой открытия следующей строки. По сути, этот показатель определяет то время, которое необходимо для чтения первого бита памяти при другой активной строке: TRP + TRCD + CL.

Row Precharge Delay. Данный параметр определяет время повторной выдачи сигнала RAS. За это время контроллер памяти способен повторно выдать сигнал инициализации адреса строки.

tRCD — это количество тактов между командой открытия строки и непосредственным доступом к ее столбцам. Данный показатель включает в себя время, которое необходимо для чтения первого бита памяти, без активной строки: TRCD + CL.

Данный показатель включает в себя время, которое необходимо для чтения первого бита памяти, без активной строки: TRCD + CL.

RAS to CAS Delay — время задержки между определяющими сигналами адреса строки/столбца.

tRAS — это количество тактов между командой на открытие банка и командой на заряд. Это то время которое требуется на обновление строки. Данный показатель сочетается с показателем TRCD.

Activate to Precharge Delay — минимальное число циклов между активацией (RAS) и подзарядкой (Precharge) одного и того же банка памяти.

Данный показатель обозначает временную задержку между отправкой адреса строки/столбца в память и моментом запуска процесса передачи данных. Это время, которое необходимо для чтения первого бита памяти при открытой нужной строке.

CAS — число тактов от момента запроса данных до момента их считывания. Является одной из ключевых характеристик модуля памяти. По сути, данный показатель определяет ее быстродействие. Чем ниже показатель CL, тем выше работоспособность памяти.

Является одной из ключевых характеристик модуля памяти. По сути, данный показатель определяет ее быстродействие. Чем ниже показатель CL, тем выше работоспособность памяти.

Распиновка разъёмов оперативной памяти SIMM, SDRAM, RDRAM, DDR1, DDR2, DDR3

- Список рубрик

- Теги этой статьи

- ddr1

- ddr2

- ddr3

- rdram

- sdram

- simm

- оперативная

- память

- разъём

- распиновка

- Самые популярные статьи

- Новые статьи на сайте

07/10/2017

18.0 K

ddr1, ddr2, ddr3, rdram, sdram, simm, оперативная

Память DDR SDRAM DIMM (184 pin, Unbuffered)

Модуль памяти DDR SDRAM DIMM (184 pin, Unbuffered)

Нажмите для увеличения изображения

Нажмите для увеличения изображения

Распиновка разъёма DDR SDRAM DIMM (184 pin, Unbuffered)

| Slot pin # | Name | Description |

|---|---|---|

| 1 | VREF | Power supply for reference |

| 2 | DQ0 | Data input / output |

| 3 | VSS | Ground |

| 4 | DQ1 | Data input / output |

| 5 | DQS0 | Data strobe input / output |

| 6 | DQ2 | Data input / output |

| 7 | VDD | Power supply (2,5V) |

| 8 | DQ3 | Data input / output |

| 9 | NC | Not connected |

| 10 | NC | Not connected |

| 11 | VSS | Ground |

| 12 | DQ8 | Data input / output |

| 13 | DQ9 | Data input / output |

| 14 | DQS1 | Data strobe input / output |

| 15 | VDD | Power supply (2,5V) |

| 16 | CK1 | Clock input |

| 17 | CK1# | Clock input |

| 18 | VSS | Ground |

| 19 | DQ10 | Data input / output |

| 20 | DQ11 | Data input / output |

| 21 | CKE0 | Clock enable input |

| 22 | VDD | Power supply (2,5V) |

| 23 | DQ16 | Data input / output |

| 24 | DQ17 | Data input / output |

| 25 | DQS2 | Data strobe input / output |

| 26 | VSS | Ground |

| 27 | A9 | Address input (multiplexed) |

| 28 | DQ18 | Data input / output |

| 29 | A7 | Address input (multiplexed) |

| 30 | VDD | Power supply (2,5V) |

| 31 | DQ19 | Data input / output |

| 32 | A5 | Address input (multiplexed) |

| 33 | DQ24 | Data input / output |

| 34 | VSS | Ground |

| 35 | DQ25 | Data input / output |

| 36 | DQS3 | Data strobe input / output |

| 37 | A4 | Address input (multiplexed) |

| 38 | VDD | Power supply (2,5V) |

| 39 | DQ26 | Data input / output |

| 40 | DQ27 | Data input / output |

| 41 | A2 | Address input (multiplexed) |

| 42 | VSS | Ground |

| 43 | A1 | Address input (multiplexed) |

| 44 | CB0 | Not connected |

| 45 | CB1 | Not connected |

| 46 | VDD | Power supply (2,5V) |

| 47 | DQS8 | Data strobe input / output |

| 48 | A0 | Address input (multiplexed) |

| 49 | CB2 | Not connected |

| 50 | VSS | Ground |

| 51 | CB3 | Not connected |

| 52 | BA1 | Bank select address |

| 53 | DQ32 | Data input / output |

| 54 | VDD | Power supply (2,5V) |

| 55 | DQ33 | Data input / output |

| 56 | DQS4 | Data strobe input / output |

| 57 | DQ34 | Data input / output |

| 58 | VSS | Ground |

| 59 | BA0 | Bank select address |

| 60 | DQ35 | Data input / output |

| 61 | DQ40 | Data input / output |

| 62 | VDD | Power supply (2,5V) |

| 63 | WE# | Write enable |

| 64 | DQ41 | Data input / output |

| 65 | CAS# | Column address strobe |

| 66 | VSS | Ground |

| 67 | DQS5 | Data strobe input / output |

| 68 | DQ42 | Data input / output |

| 69 | DQ43 | Data input / output |

| 70 | VDD | Power supply (2,5V) |

| 71 | NC | Not connected |

| 72 | DQ48 | Data input / output |

| 73 | DQ49 | Data input / output |

| 74 | VSS | Ground |

| 75 | CK2# | Clock input |

| 76 | CK2 | Clock input |

| 77 | VDD | Power supply (2,5V) |

| 78 | DQS6 | Data strobe input / output |

| 79 | DQ50 | Data input / output |

| 80 | DQ51 | Data input / output |

| 81 | VSS | Ground |

| 82 | NC | Not connected |

| 83 | DQ56 | Data input / output |

| 84 | DQ57 | Data input / output |

| 85 | VDD | Power supply (2,5V) |

| 86 | DQS7 | Data strobe input / output |

| 87 | DQ58 | Data input / output |

| 88 | DQ59 | Data input / output |

| 89 | VSS | Ground |

| 90 | NC | Not connected |

| 91 | SDA | Serial data I/O |

| 92 | SCL | Serial clock |

| 93 | VSS | Ground |

| 94 | DQ4 | Data input / output |

| 95 | DQ5 | Data input / output |

| 96 | VDD | Power supply (2,5V) |

| 97 | DQS9 | Data strobe input / output |

| 98 | DQ6 | Data input / output |

| 99 | DQ7 | Data input / output |

| 100 | VSS | Ground |

| 101 | NC | Not connected |

| 102 | NC | Not connected |

| 103 | NC | Not connected |

| 104 | VDD | Power supply (2,5V) |

| 105 | DQ12 | Data input / output |

| 106 | DQ13 | Data input / output |

| 107 | DQS10 | Data strobe input / output |

| 108 | VDD | Power supply (2,5V) |

| 109 | DQ14 | Data input / output |

| 110 | DQ15 | Data input / output |

| 111 | CKE1 | Clock enable input |

| 112 | VDD | Power supply (2,5V) |

| 113 | NC | Not connected |

| 114 | DQ20 | Data input / output |

| 115 | A12 | Address input (multiplexed) |

| 116 | VSS | Ground |

| 117 | DQ21 | Data input / output |

| 118 | A11 | Address input (multiplexed) |

| 119 | DQS11 | Data strobe input / output |

| 120 | VDD | Power supply (2,5V) |

| 121 | DQ22 | Data input / output |

| 122 | A8 | Address input (multiplexed) |

| 123 | DQ23 | Data input / output |

| 124 | VSS | Ground |

| 125 | A6 | Address input (multiplexed) |

| 126 | DQ28 | Data input / output |

| 127 | DQ29 | Data input / output |

| 128 | VDD | Power supply (2,5V) |

| 129 | DQS12 | Data strobe input / output |

| 130 | A3 | Address input (multiplexed) |

| 131 | DQ30 | Data input / output |

| 132 | VSS | Ground |

| 133 | DQ31 | Data input / output |

| 134 | CB4 | Not connected |

| 135 | CB5 | Not connected |

| 136 | VDD | Power supply (2,5V) |

| 137 | CK0 | Clock input |

| 138 | CK0# | Clock input |

| 139 | VSS | Ground |

| 140 | DQS17 | Data strobe input / output |

| 141 | A10 | Address input (multiplexed) |

| 142 | CB6 | Not connected |

| 143 | VDD | Power supply (2,5V) |

| 144 | CB7 | Not connected |

| 145 | VSS | Ground |

| 146 | DQ36 | Data input / output |

| 147 | DQ37 | Data input / output |

| 148 | VDD | Power supply (2,5V) |

| 149 | DQS13 | Data strobe input / output |

| 150 | DQ38 | Data input / output |

| 151 | DQ39 | Data input / output |

| 152 | VSS | Ground |

| 153 | DQ44 | Data input / output |

| 154 | RAS# | Row address strobe |

| 155 | DQ45 | Data input / output |

| 156 | VDD | Power supply (2,5V) |

| 157 | S0# | Chip select input |

| 158 | S1# | Chip select input |

| 159 | DQS14 | Data strobe input / output |

| 160 | VSS | Ground |

| 161 | DQ46 | Data input / output |

| 162 | DQ47 | Data input / output |

| 163 | NC | Not connected |

| 164 | VDD | Power supply (2,5V) |

| 165 | DQ52 | Data input / output |

| 166 | DQ53 | Data input / output |

| 167 | NC | Not connected |

| 168 | VDD | Power supply (2,5V) |

| 169 | DQS15 | Data strobe input / output |

| 170 | DQ54 | Data input / output |

| 171 | DQ55 | Data input / output |

| 172 | VDD | Power supply (2,5V) |

| 173 | NC | Not connected |

| 174 | DQ60 | Data input / output |

| 175 | DQ61 | Data input / output |

| 176 | VSS | Ground |

| 177 | DQS16 | Data strobe input / output |

| 178 | DQ62 | Data input / output |

| 179 | DQ63 | Data input / output |

| 180 | VDD | Power supply (2,5V) |

| 181 | SA0 | Address in EEPROM |

| 182 | SA1 | Address in EEPROM |

| 183 | SA2 | Address in EEPROM |

| 184 | VDDSPD | Serial EEPROM power supply (2,3-3,6V) |

Память DDR2 SDRAM DIMM Unbuffered Module (240 pin)

Модуль памяти DDR2 SDRAM DIMM (240 pin, Unbuffered)

Нажмите для увеличения изображения

Разъём 240 pin DDR2

Нажмите для увеличения изображения

Распиновка разъёма 240 pin DDR2

| Контакт # | Описание | Контакт # | Описание |

|---|---|---|---|

| 1 | VREF | 121 | VSS |

| 2 | VSS | 122 | DQ4 |

| 3 | DQ0 | 123 | DQ5 |

| 4 | DQ1 | 124 | VSS |

| 5 | VSS | 125 | DM0 |

| 6 | /DQS0 | 126 | NC |

| 7 | DQS0 | 127 | VSS |

| 8 | VSS | 128 | DQ6 |

| 9 | DQ2 | 129 | DQ7 |

| 10 | DQ3 | 130 | VSS |

| 11 | VSS | 131 | DQ12 |

| 12 | DQ8 | 132 | DQ13 |

| 13 | DQ9 | 133 | VSS |

| 14 | VSS | 134 | DM1 |

| 15 | /DQS1 | 135 | NC |

| 16 | DQS1 | 136 | VSS |

| 17 | VSS | 137 | CK1 |

| 18 | NC | 138 | /CK1 |

| 19 | NC | 139 | VSS |

| 20 | VSS | 140 | DQ14 |

| 21 | DQ10 | 141 | DQ15 |

| 22 | DQ11 | 142 | VSS |

| 23 | VSS | 143 | DQ20 |

| 24 | DQ16 | 144 | DQ21 |

| 25 | DQ17 | 145 | VSS |

| 26 | VSS | 146 | DM2 |

| 27 | /DQS2 | 147 | NC |

| 28 | DQS2 | 148 | VSS |

| 29 | VSS | 149 | DQ22 |

| 30 | DQ18 | 150 | DQ23 |

| 31 | DQ19 | 151 | VSS |

| 32 | VSS | 152 | DQ28 |

| 33 | DQ24 | 153 | DQ29 |

| 34 | DQ25 | 154 | VSS |

| 35 | VSS | 155 | DM3 |

| 36 | /DQS3 | 156 | NC |

| 37 | DQS3 | 157 | VSS |

| 38 | VSS | 158 | DQ30 |

| 39 | DQ26 | 159 | DQ31 |

| 40 | DQ27 | 160 | VSS |

| 41 | VSS | 161 | NC |

| 42 | NC | 162 | NC |

| 43 | NC | 163 | VSS |

| 44 | VSS | 164 | NC |

| 45 | NC | 165 | NC |

| 46 | NC | 166 | VSS |

| 47 | VSS | 167 | NC |

| 48 | NC | 168 | NC |

| 49 | NC | 169 | VSS |

| 50 | VSS | 170 | VDDQ |

| 51 | VDDQ | 171 | CKE1 |

| 52 | CKE0 | 172 | VDD |

| 53 | VDD | 173 | NC |

| 54 | NC | 174 | NC |

| 55 | NC | 175 | VDDQ |

| 56 | VDDQ | 176 | A12 |

| 57 | A11 | 177 | A9 |

| 58 | A7 | 178 | VDD |

| 59 | VDD | 179 | A8 |

| 60 | A5 | 180 | A6 |

| 61 | A4 | 181 | VDDQ |

| 62 | VDDQ | 182 | A3 |

| 63 | A2 | 183 | A1 |

| 64 | VDD | 184 | VDD |

| KEY (Ключ) | |||

| 65 | VSS | 185 | CK0 |

| 66 | VSS | 186 | /CK0 |

| 67 | VDD | 187 | VDD |

| 68 | NC | 188 | A0 |

| 69 | VDD | 189 | VDD |

| 70 | A10/AP | 190 | BA1 |

| 71 | BA0 | 191 | VDDQ |

| 72 | VDDQ | 192 | /RAS |

| 73 | /WE | 193 | /CS0 |

| 74 | /CAS | 194 | VDDQ |

| 75 | VDDQ | 195 | ODT0 |

| 76 | /CS1 | 196 | A13 |

| 77 | ODT1 | 197 | VDD |

| 78 | VDDQ | 198 | VSS |

| 79 | VSS | 199 | DQ36 |

| 80 | DQ32 | 200 | DQ37 |

| 81 | DQ33 | 201 | VSS |

| 82 | VSS | 202 | DM4 |

| 83 | /DQS4 | 203 | NC |

| 84 | DQS4 | 204 | VSS |

| 85 | VSS | 205 | DQ38 |

| 86 | DQ34 | 206 | DQ39 |

| 87 | DQ35 | 207 | VSS |

| 88 | VSS | 208 | DQ44 |

| 89 | DQ40 | 209 | DQ45 |

| 90 | DQ41 | 210 | VSS |

| 91 | VSS | 211 | DM5 |

| 92 | /DQS5 | 212 | NC |

| 93 | DQS5 | 213 | VSS |

| 94 | VSS | 214 | DQ46 |

| 95 | DQ42 | 215 | DQ47 |

| 96 | DQ43 | 216 | VSS |

| 97 | VSS | 217 | DQ52 |

| 98 | DQ48 | 218 | DQ53 |

| 99 | DQ49 | 219 | VSS |

| 100 | VSS | 220 | CK2 |

| 101 | SA2 | 221 | /CK2 |

| 102 | NC | 222 | VSS |

| 103 | VSS | 223 | DM6 |

| 104 | /DQS6 | 224 | NC |

| 105 | DQS6 | 225 | VSS |

| 106 | VSS | 226 | DQ54 |

| 107 | DQ50 | 227 | DQ55 |

| 108 | DQ51 | 228 | VSS |

| 109 | VSS | 229 | DQ60 |

| 110 | DQ56 | 230 | DQ61 |

| 111 | DQ57 | 231 | VSS |

| 112 | VSS | 232 | DM7 |

| 113 | /DQS7 | 233 | NC |

| 114 | DQS7 | 234 | VSS |

| 115 | VSS | 235 | DQ62 |

| 116 | DQ58 | 236 | DQ63 |

| 117 | DQ59 | 237 | VSS |

| 118 | VSS | 238 | VDDSPD |

| 119 | SDA | 239 | SA0 |

| 120 | SCL | 240 | SA1 |

Описание контактов и другую информацию по распиновке DDR2 можно найти в документации к модулям памяти DDR2 Micron.

Память DDR3 SDRAM DIMM Unbuffered Module (240 pin)

Модуль памяти DDR3 SDRAM DIMM (240 pin, Unbuffered)

Нажмите для увеличения изображения

Разъём 240 pin DDR3

Нажмите для увеличения изображения

Описание контактов и другую информацию по распиновке можно найти в документации к модулям памяти DDR3 Micron.

Распиновка разъёма 240 pin DDR3

Нажмите для увеличения изображения

Источник: radio-hobby.org

Теги этой статьи

- ddr1

- ddr2

- ddr3

- rdram

- sdram

- simm

- оперативная

- память

- разъём

- распиновка

Близкие по теме статьи:

Проверяем microSD SD карты памяти, реальный объём, скорость чтения и записи

6.5 K

h3testw, microsd, usb, карта, память, флэшка

Читать

Распиновка оперативной памяти DDR4 для настольных ПК

9. 5 K

5 K

ddr4, земля, контакты, общий, оперативки, памяти, питание

Читать

Распиновка разъёмов матриц для ноутбуков. 20pin, 30 pin, 40pin, 50pin.

18.4 K

20pin, 30pin, 40pin, 50pin, pinouts, матрица, ноутбук

Читать

Распиновка разъёмов оперативной памяти ноутбука. (SIMM, SDRAM, RDRAM, DDR1, DDR2, DDR3)

6.7 K

ddr, ddr2, ddr3, dimm, microdimm, pc100, pc133

Читать

Типы оперативной памяти. Память небуферизированная, память с ECC, память регистровая с ECC. В чём отличия.

21.9 K

ecc, memory, registered, буфер, микросхем, ошибок, память

Читать

Интересное в новостях

04/08/2022 12:50

514

Из Крыма приехали волонтёры в Мариуполь и привезли гуманитарную помощь для оставшихся в городе жителей, немного пообщались с пожилыми жителями города, мамочками с детьми и другими, кто нуждается в помощи….

Читать полностью

26/07/2022 10:20

542

Украинский город Северодонецк российские войска «освободили» как Мариуполь. Июль 2022. Смотрим. Разрушения в Северодонеце наглядно демонстрируют, на что способна безжалостная российская артиллерия….

Июль 2022. Смотрим. Разрушения в Северодонеце наглядно демонстрируют, на что способна безжалостная российская артиллерия….

Читать полностью

22/07/2022 13:45

713

1. Приморский район, Черёмушки, часть первая 2. Приморский район, Черёмушки, часть вторая 3. Центральный район, Драмтеатр, улица Куинджи (Артёма) 4. Центральный район, рынок Азовский, МЖК, улица…

Читать полностью

Компьютерный мирSector

Вся информация на страницах сайта предназначена только для личного не коммерческого использования, учёбы, повышения квалификации и не включает призывы к каким либо действиям.

Частичное или полное использование материалов сайта разрешается только при условии добавления ссылки на непосредственный адрес материала на нашем сайте.

Это интересно

Оперативная память

DDR1, DDR2, DDR3 и DDR4: в чем их различия?

С момента появления оперативной памяти в формате DIMM (Dual In-line Memory Module) на рынке появилось много типов памяти, но с 2000 года именно память DDR преобладает над остальными.

Здесь мы расскажем о разнице между DDR1, DDR2, DDR3 и DDR4 с момента ее появления в 2000 году.

Это правда, что оперативная память DDR1 и DDR2 больше не используется, и фактически памяти DDR1 уже давно нет. Оперативная память DDR3 больше не выпускается, но многие все еще используют ее, в то время как DDR4 уже утвердилась на рынке с момента ее запуска в 2014 году и в настоящее время используется на всех платформах.

Но давайте посмотрим, какие различия мы находим между оперативной памятью DDR1, DDR2, DDR3 и DDR4, чтобы вы могли научиться различать эти типы модулей.

Содержание

Технические отличия

DDR расшифровывается как Double Data Rate, и в основном это означает, что они способны выполнять две задачи чтения и две задачи записи за такт. Это то, что объединяет все поколения, но логически каждое новое поколение вносит изменения и улучшения, которые делают их технически очень разными.

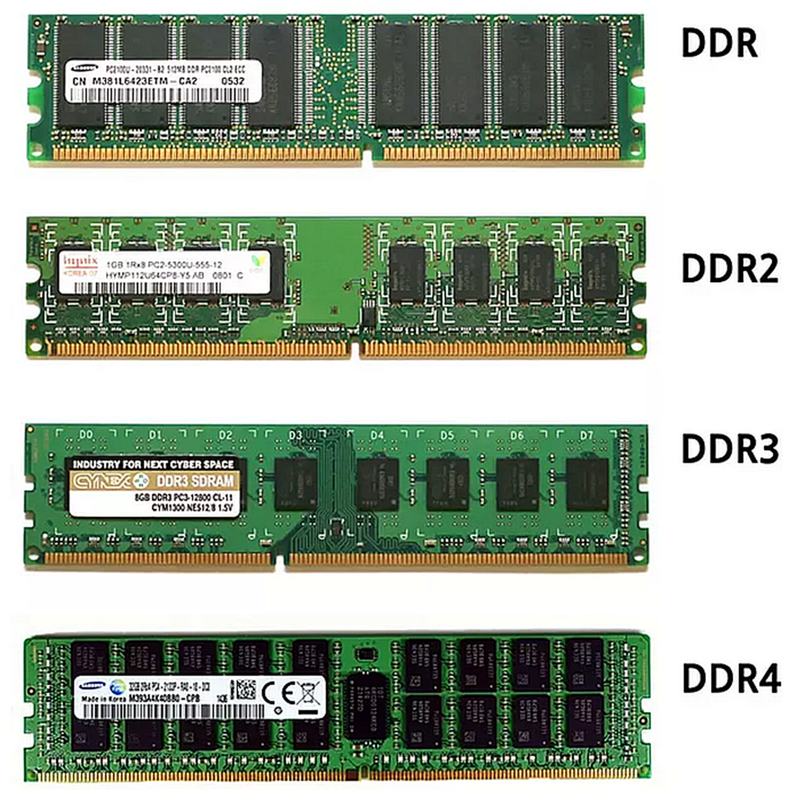

Оперативная память DDR1

Выпущена в 2000 году, не использовалась почти до 2002 года. скорость 266 МТ/с (100-200 МГц).

скорость 266 МТ/с (100-200 МГц).

ОЗУ DDR2

Выпущенный примерно в 2004 году, он работал при напряжении 1,8 В, что на 28% меньше, чем у DDR1. Его максимальная плотность была удвоена до 256 Мб (2 Гб на модуль). Логично, что и максимальная скорость приумножилась, достигнув 533 МГц.

ОЗУ DDR3

Этот выпуск вышел в 2007 году, и это была революция, потому что здесь были реализованы профили XMP. Начнем с того, что модули памяти работали при напряжении 1,5 В и 1,65 В с базовой частотой 1066 МГц, но дело пошло гораздо дальше, и плотность достигла 8 ГБ на модуль.

Оперативная память DDR4

Это не появлялось до 2014 года, но сегодня оно уже является самым распространенным. Напряжение снижено до 1,05 и 1,2В, хотя многие модули работают при 1,35В. Скорость была заметно увеличена, и с каждым разом с завода выпускается более быстрая память, но ее базовая частота начиналась с 2133 МГц. На данный момент уже есть модули на 32 Гб, но и это понемногу расширяется.

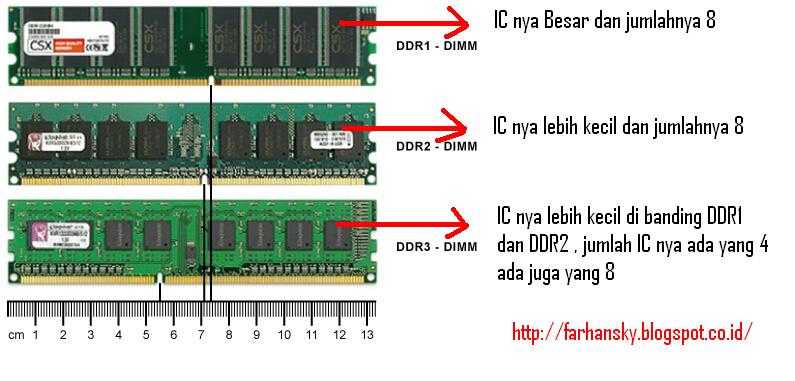

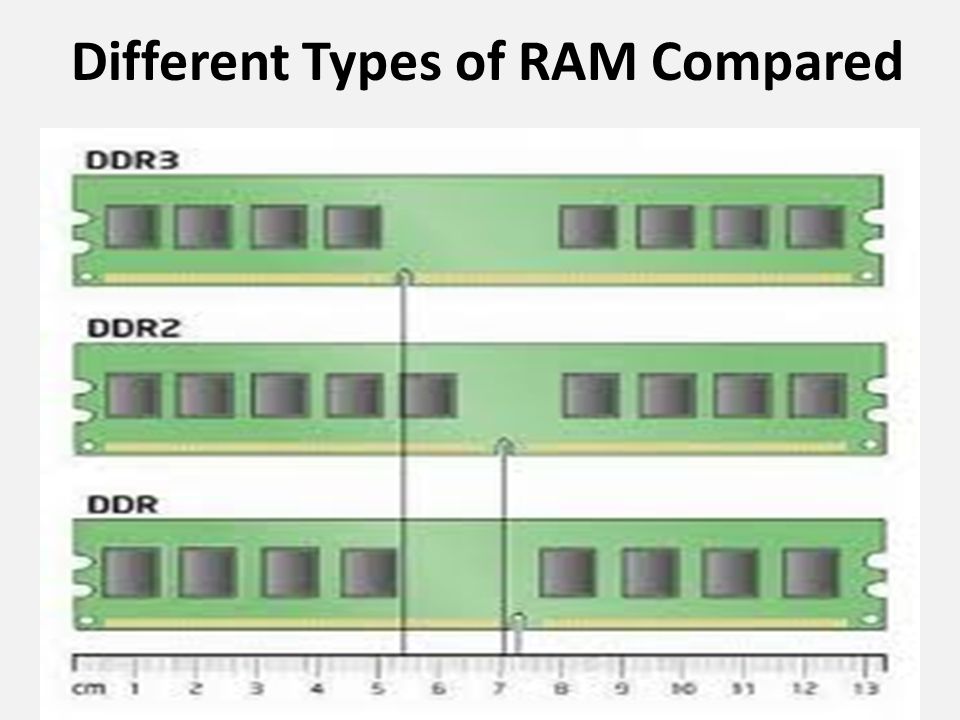

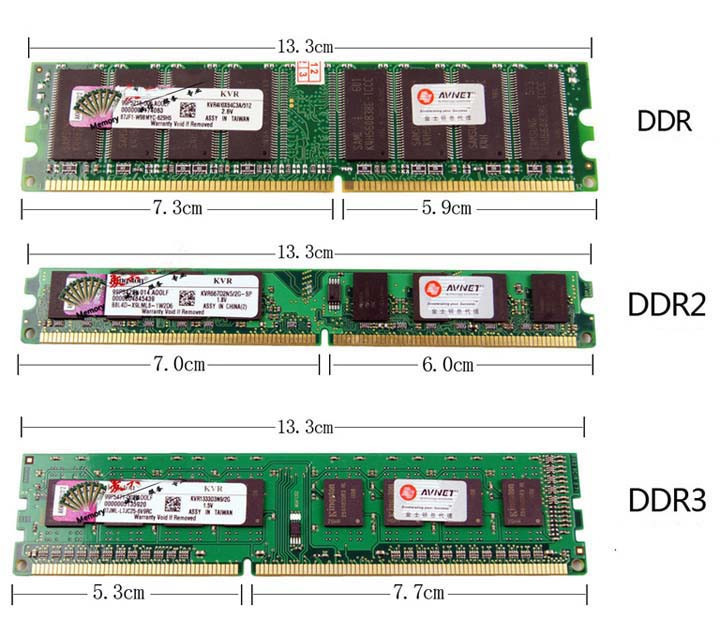

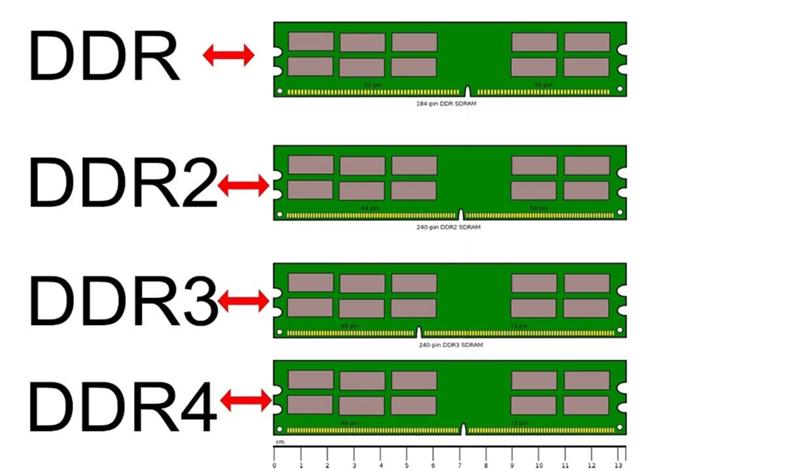

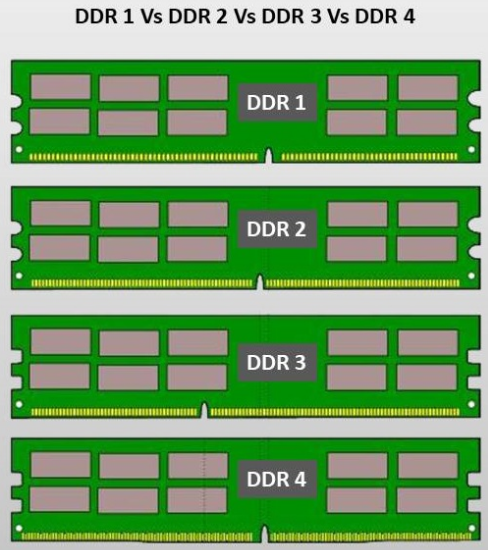

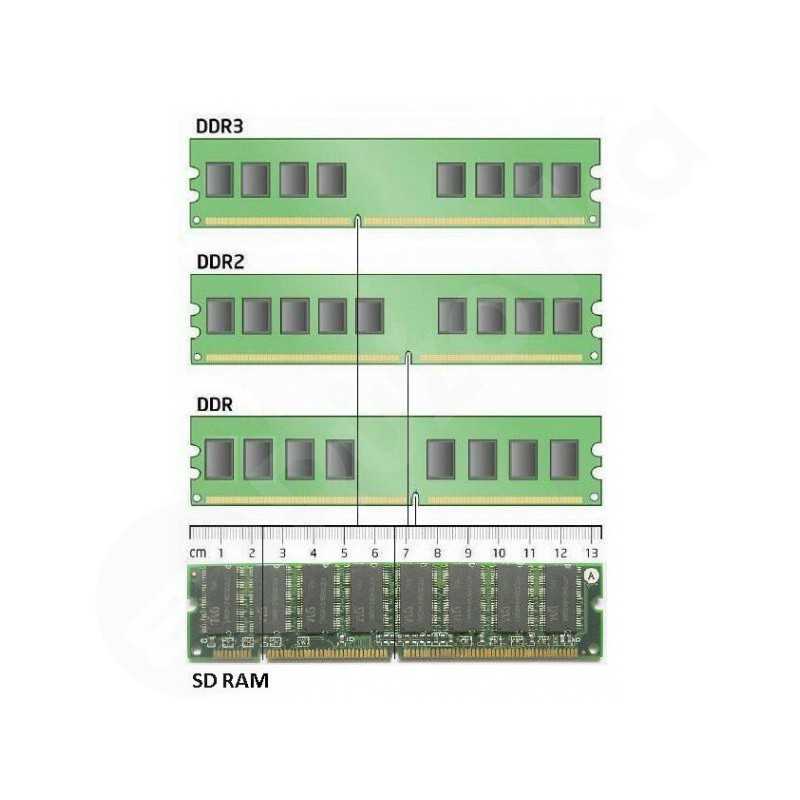

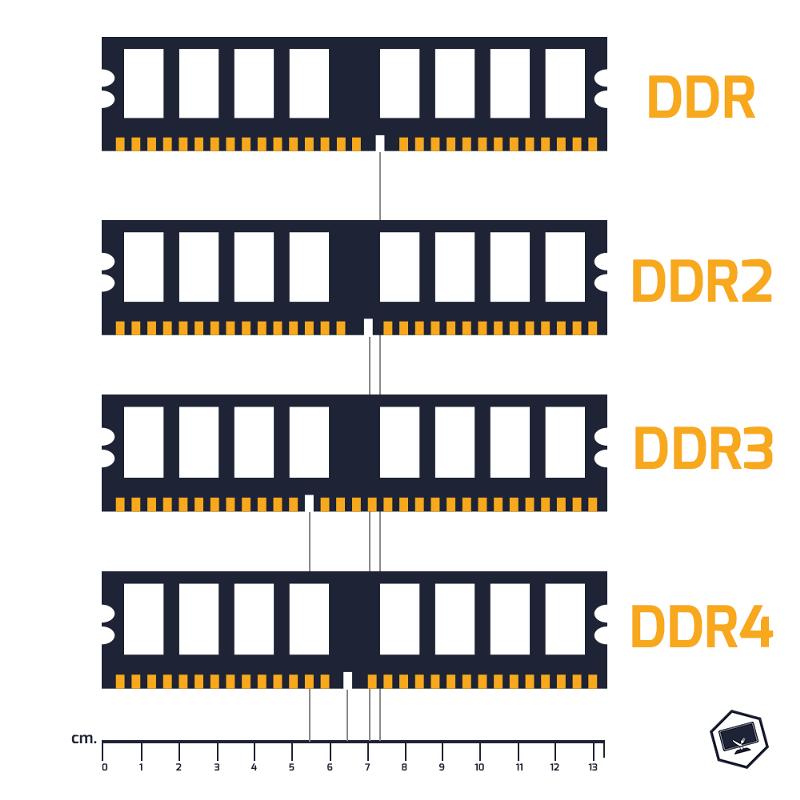

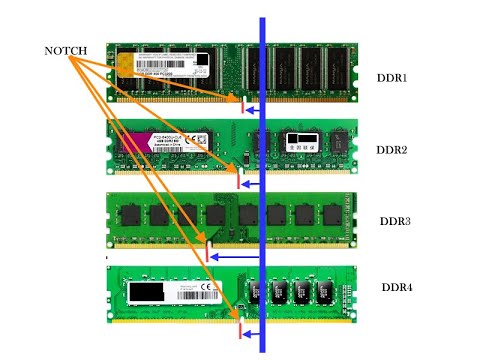

Физические различия

Хотя эти четыре типа памяти имеют формат DIMM и могут выглядеть очень похоже (на самом деле все они имеют длину 133,35 мм). Существуют фундаментальные физические различия, из-за которых мы никогда не сможем подключить модуль оперативной памяти DDR1 к разъему DDR2.

Все модули имеют отверстие в районе контактов, которое предотвратит их подключение к розеткам другого поколения (и будьте осторожны, потому что если вы нажмете слишком сильно, вы можете сломать розетку или модуль оперативной памяти).

Кроме того, модули памяти DDR4 RAM имеют контактную площадку с выступом в центре. Он не совсем плоский, хотя и не нужен, потому что разрез не позволит нам подключить модуль DDR4 в сокет другого поколения. На изображении, приведенном ниже, вы можете увидеть физические различия в каждом модуле.

Наконец, следует отметить, что в каждом поколении количество контактов менялось следующим образом:

- DDR1: 184 контакта (DIMM), 200 контактов (SO-DIMM) и 172 контакта (микро DIMM).

- DDR2: 240-контактный (DIMM), 200-контактный (SO-DIMM) и 214-контактный (микро-DIMM).

- DDR3: 240 контактов (DIMM), 204 контакта (SO-DIMM) и 214 контактов (micro DIMM).

- DDR4: 288-контактный (DIMM), 256-контактный (SO-DIMM). Модули памяти DDR4 micro DIMM больше не существуют.

Различия в производительности оперативной памяти

Наиболее очевидные различия между различными поколениями оперативной памяти заключаются в производительности. По мере развития технологий производительность постепенно улучшалась, и, как правило, она удваивалась от поколения к поколению.

Таким образом, очевидна разница между оперативной памятью DDR3 и DDR4 например, и не только в практическом плане, но и в плане ощущений, которые пользователи оценивают при использовании ПК с той или иной памятью.

Однако это правда, что также связано с улучшением производительности остальных компонентов, поскольку переход от одного поколения оперативной памяти к другому обычно связан с полной сменой платформы.

Надеюсь, статья помогла понять разницу между DDR1, DDR2, DDR3 и DDR4. Поэтому, если вы когда-нибудь задумаетесь об обновлении оперативной памяти на своем ПК, не забудьте проверить характеристики материнской платы, чтобы узнать, какой тип оперативной памяти она поддерживает.

Узнайте о модулях компьютерной памяти — centonelectronics

SDRAM является синхронной, поэтому для синхронизации сигналов используются часы, создавая предсказуемые упорядоченные циклы выборки и записи данных. Однако SDRAM передает данные по одному фронту тактовой частоты. DDR SDRAM означает, что этот тип SDRAM извлекает данные как по переднему, так и по заднему фронту тактового сигнала, который регулирует его, отсюда и название «Двойная скорость передачи данных». До DDR RAM извлекала данные только один раз за такт. Синхронные данные обеспечивают более быструю работу при координации выборки памяти с требованиями процессора.

Многие люди называют оперативную память процессора просто «DDR», используя эти термины взаимозаменяемо, поскольку DDR так широко используется в качестве оперативной памяти процессора с конца 1990-х годов. DDR — это не флэш-память, подобная той, которая используется для твердотельных накопителей (SSD), карт Secure Digital (SD) или накопителей с универсальной последовательной шиной (USB). Память DDR энергозависима, что означает, что она теряет все при отключении питания.

DDR — это не флэш-память, подобная той, которая используется для твердотельных накопителей (SSD), карт Secure Digital (SD) или накопителей с универсальной последовательной шиной (USB). Память DDR энергозависима, что означает, что она теряет все при отключении питания.

Оперативная память DDR1

Выпущена в 2000 году, не использовалась почти до 2002 года. ) со скоростью 266 МТ/с (100-200 МГц).

ОЗУ DDR2

Выпущенный примерно в 2004 году, он работал при напряжении 1,8 В, что на 28% меньше, чем у DDR1. Его максимальная плотность была удвоена до 256 Мб (2 Гб на модуль). Логично, что и максимальная скорость приумножилась, достигнув 533 МГц.

ОЗУ DDR3

Этот выпуск вышел в 2007 году, и здесь были реализованы профили XMP. Начнем с того, что модули памяти работали при напряжении 1,5 В и 1,65 В, с базовой частотой 1066 МГц, а плотность достигала 8 ГБ на модуль.

• (XMP или Extreme Memory Profiles — это технология Intel, которая позволяет изменять несколько параметров памяти, просто выбирая другой профиль, используя более высокие скорости памяти, чем стандартные)

ОЗУ DDR4

Это не поступать до 2014 года, но на сегодняшний день он является самым распространенным. Напряжение снижено до 1,05 и 1,2В, хотя многие модули работают при 1,35В. Скорость была заметно увеличена, и с каждым разом с завода выпускается более быстрая память, но ее базовая частота начиналась с 2133 МГц. На данный момент уже есть модули на 32 Гб, но и это понемногу расширяется.

Напряжение снижено до 1,05 и 1,2В, хотя многие модули работают при 1,35В. Скорость была заметно увеличена, и с каждым разом с завода выпускается более быстрая память, но ее базовая частота начиналась с 2133 МГц. На данный момент уже есть модули на 32 Гб, но и это понемногу расширяется.

Стандарт

Рабочее напряжение

Асвязанные тактовые циклы ОЗУ

DDR SDRAM (2000)

DDR2 SDRAM (2003)

DDR2DRAM (2003)

DDR2DRAM (2003)

DDR2DRAM (2003)

DDR2DRAM (20003

DDR2DRAM (20003

DDR2DRAM ) SDRAM (2014)

2,6 В, 2,5 В

1,8 В, 1,55 В

1,5 В, 1,35 В

100 — 200 МГц

200 — 400 МГц

400 МГц — 1066 МГц

1066–16002 4002 МГц — 1066 МГц

1066–16002 4002 МГц — 1066 МГц

1066 –19002 400 МГц — 1066 МГц

9000.19003

400 МГц — 1066 МГц

. МГц

МГц

Физические различия

Хотя эти четыре типа памяти имеют формат DIMM и могут выглядеть очень похоже (на самом деле все они имеют длину 133,35 мм). Существуют фундаментальные физические различия, из-за которых вы не можете подключить модуль оперативной памяти DDR1 к разъему DDR2.

Все модули имеют отверстие в области контактов, что предотвратит их подключение к розеткам другого поколения.

Наконец, следует отметить, что в каждом поколении количество контактов менялось следующим образом:

Самая большая разница от поколения к поколению оперативной памяти заключалась в производительности. По мере развития и совершенствования технологий мы обычно наблюдаем удвоение для каждого выпуска.

DDR5 SDRAM — следующий стандарт, предложенный для удвоения скорости DDR4 SDRAM. По данным Ассоциации твердотельных технологий JEDEC, которая является стандартом для DDR SDRAM, «стандарт JEDEC DDR5 в настоящее время находится в разработке в комитете JEDEC JC-42 по твердотельным запоминающим устройствам.