Сигнальный процессор что это: Цифровой сигнальный процессор/DSP

Содержание

Цифровой сигнальный процессор

Цифровой сигнальный

процессор (англ. Digital

signal processor, DSP; сигнальный микропроцессор) —

специализированный микропроцессор,

предназначенный для цифровой

обработки сигналов

(обычно в реальном

масштабе времени).

Архитектура

сигнальных процессоров, по сравнению

с микропроцессорами настольных

компьютеров, имеет некоторые особенности:

Гарвардская

архитектура

(разделение памяти команд и данных),

как правило модифицированная;Большинство

сигнальных процессоров имеют встроенную

оперативную

память,

из которой может осуществляться выборка

нескольких машинных

слов

одновременно. Нередко встроено сразу

несколько видов оперативной памяти,

например, в силу Гарвардской архитектуры

бывает отдельная память для инструкций

и отдельная — для данных.Некоторые

сигнальные процессоры обладают одним

или даже несколькими встроенными

постоянными

запоминающими устройствами

с наиболее употребительными

подпрограммами, таблицами и т. п.

п.

Аппаратное

ускорение сложных вычислительных

инструкций, то есть быстрое выполнение

операций, характерных для цифровой

обработки сигналов, например, операция

«умножение с накоплением» (MAC) (Y := X + A ×

B) обычно исполняется за один такт.«Бесплатные» по

времени циклы

с заранее известной длиной. Поддержка

векторно-конвейерной обработки с

помощью генераторов адресных

последовательностей.Детерминированная

работа с известными временами выполнения

команд, что позволяет выполнять

планирование работы в реальном

времени.Сравнительно

небольшая длина конвейера,

так что незапланированные условные

переходы

могут занимать меньшее время, чем в

универсальных процессорах.Экзотический

набор регистров

и инструкций, часто сложных для

компиляторов.

Некоторые архитектуры используют VLIW.По сравнению с

микроконтроллерами,

ограниченный набор периферийных

устройств — впрочем, существуют

«переходные» чипы, сочетающие в себе

свойства DSP и широкую периферию

микроконтроллеров.

(см18 если

недостаточно)

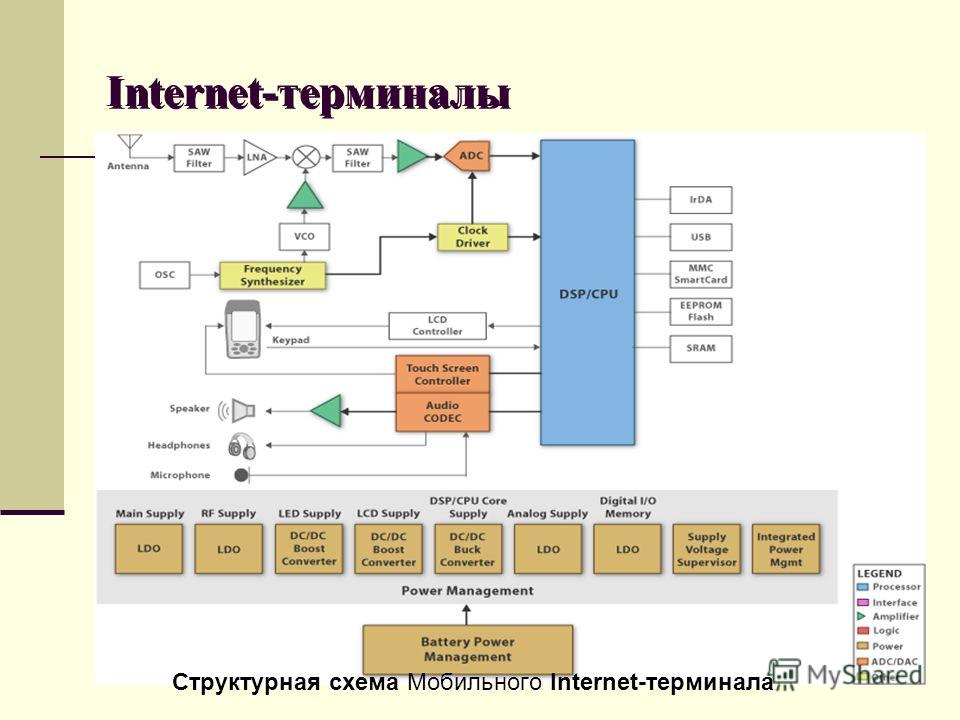

Области применения

Коммуникационное

оборудование:Системы гидро- и

радиолокации;Распознавание

речи и изображений;Речевые и музыкальные

синтезаторы;Анализаторы

спектра;Управление

технологическими процессами;Другие области,

где необходима быстродействующая

обработка сигналов, в том числе в

реальном времени.

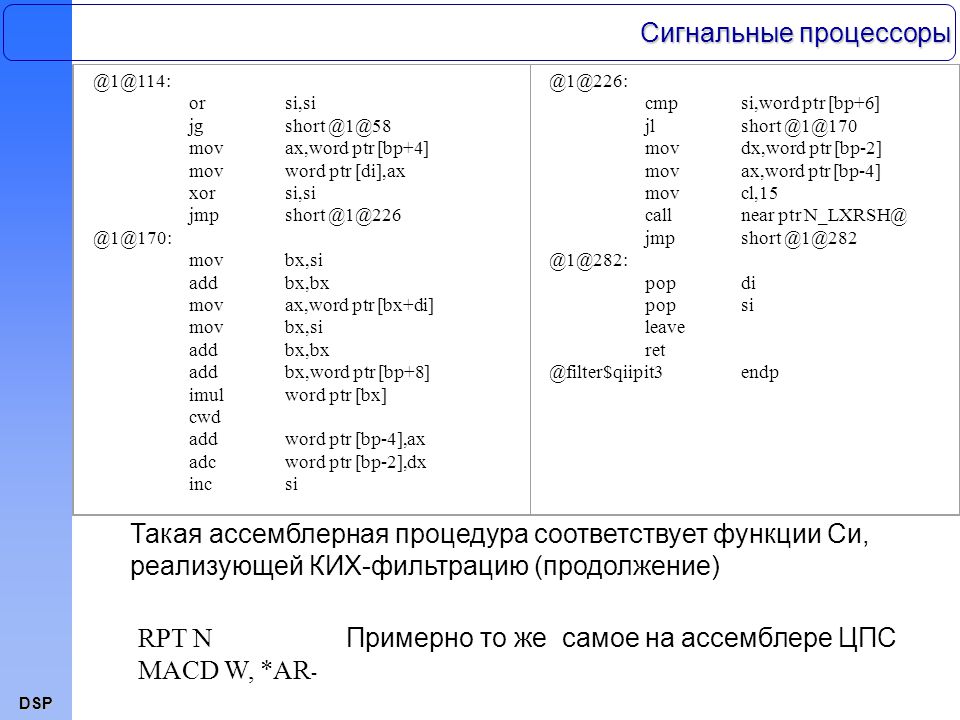

Для программирования

ЦСП обычно используют один из двух

языков — ассемблер

и C.

Основные особенности ассемблеров ЦСП

совпадают с аналогичными языками обычных

микропроцессоров

и, в целом, могут быть описаны как:

Язык ассемблера

является машинно-ориентированным, то

есть каждое семейство процессоров

имеет язык, отличающийся от языка других

семейств;Одна команда на

ассемблере обычно эквивалентна одной

команде машинного языка;При программировании

на ассемблере программисту доступны

все ресурсы процессора и системы, что

позволяет использовать их максимально

эффективно;От программиста

требуется хорошее знание архитектуры

каждого конкретного процессора, с

которым он работает, то есть требуемая

квалификация персонала должна быть

достаточно высокой;Создание и отладка

программ на ассемблере — длительный

трудоёмкий процесс, также требующий

высокой квалификации.

С другой стороны,

при использовании языков высокого

уровня, в частности, C, можно заметно

упростить и ускорить создание программ,

но при этом ресурсы системы будут

использоваться менее эффективно, по

сравнению с программой, целиком написанной

на ассемблере.

В реальности обычно

используются подход, совмещающий

достоинства как языков высокого уровня,

так и эффективности программ на

ассемблере. Выражается это в том, что

стандартные библиотеки обычно создаются

на ассемблере, как и критичные ко времени

исполнения и объёму памяти части кода.

В то же время вспомогательные модули

могут создаваться на языке высокого

уровня, ускоряя и упрощая разработку

программной системы в целом.

Цифровые процессоры обработки сигналов (Лекция) | МПС

МПС

Цифровые процессоры обработки

сигналов (Лекция)

ПЛАН ЛЕКЦИИ

1. Общая структура цифровой

обработки сигналов

2. Структура процессоров цифровой

Структура процессоров цифровой

обработки сигналов

3. Основные показатели процессоров цифровой обработки сигналов

4. Основные производители сигнальных процессоров

5. Аппаратная реализация

1. Общая структура цифровой обработки

сигналов

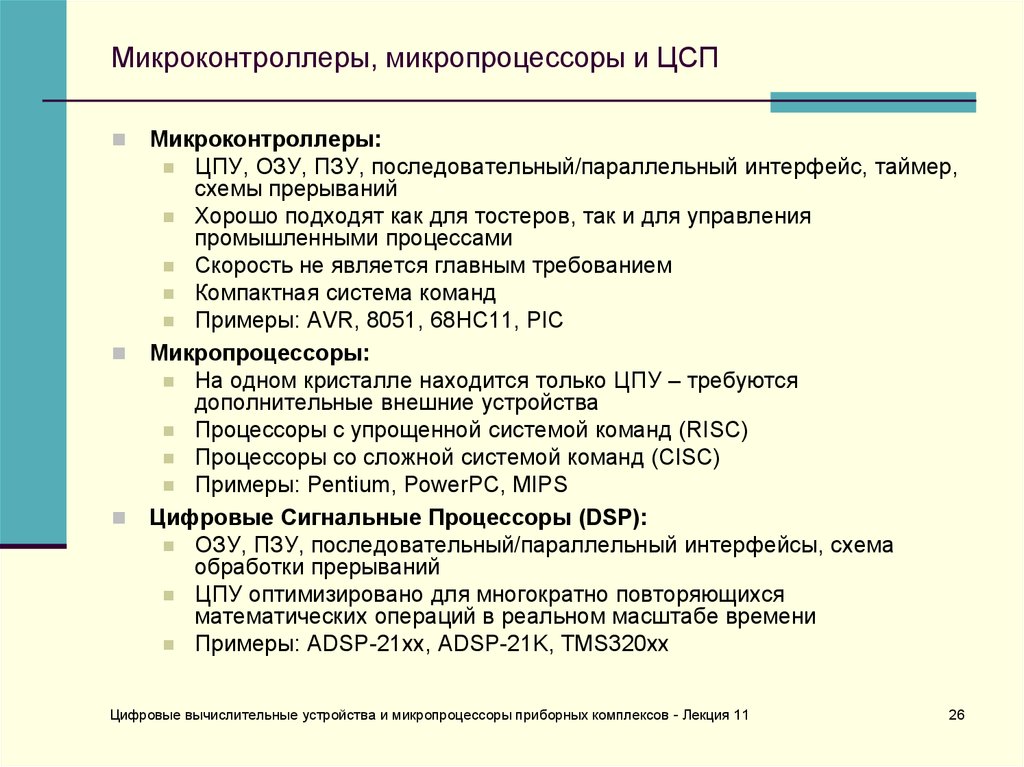

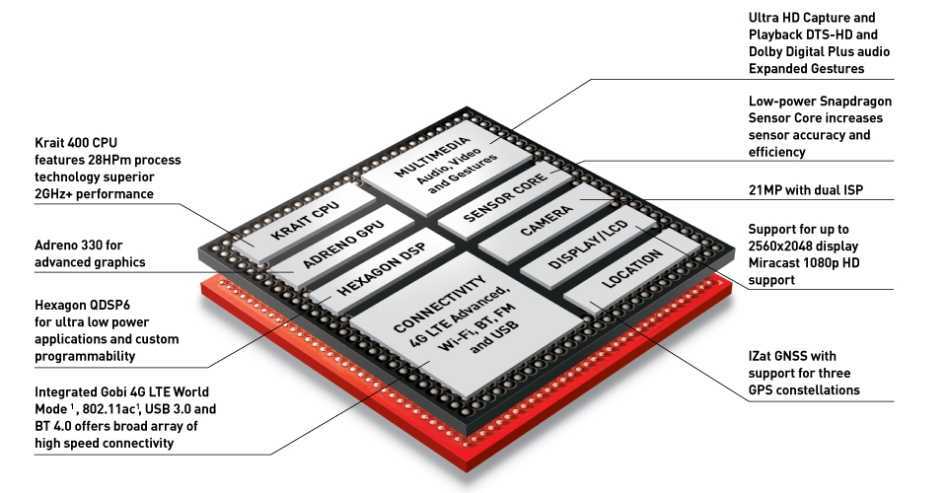

Цифровые

процессоры обработки сигналов (ЦПОС) или их равнозначное название – цифровые сигнальные

процессоры (ЦСП или просто сигнальные процессоры), англоязычное сокращение – DSP (Digital Signal Processor), предназначены для

реализации алгоритмов цифровой обработки сигналов (ЦОС) и систем управления в

реальном времени.

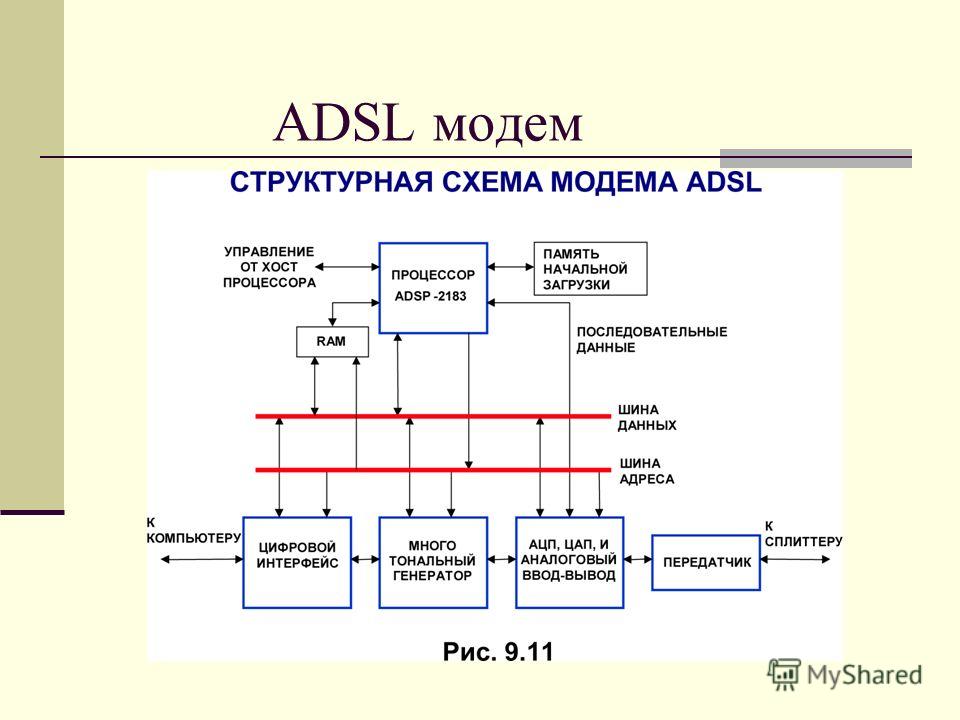

Схема цифровой обработки аналоговых сигналов.

Кодер формирует последовательность

чисел, соответствующую обрабатываемому аналоговому сигналу.

Декодер по

принятому сигналу формирует аналоговый сигнал, то есть производит преобразования,

обратные происходившим в кодере.

На вход

системы поступает ограниченный по длительности сигнал x(t). В силу конечной длительности сигнала его спектр бесконечен.

Аналого-цифровое

преобразование осуществляется в два этапа: дискретизации по времени и квантования

по уровню.

Дискретизация – это процедура взятия

мгновенных значений сигнала x(t) через равные промежутки

времени Т. Мгновенные значения x(nТ) называются выборками,

время Т – период дискретизации, а n — указывает порядковый номер отсчета. Чем чаще брать отсчеты,

тем меньше период дискретизации Т, тем точнее последовательность отсчетов x(nТ) будет изображать исходный сигнал x (t).

Период дискретизации Т определяет

частоту дискретизации:

fд =; Т =

Из формул видно, что чем меньше Т, тем выше частота дискретизации fд, а чем выше частота дискретизации, тем труднее вычислителю

выполнять большое количество операций над отсчетами в темпе их поступления на

переработку и тем сложнее должно быть устройство. Таким образом, точность представления

Таким образом, точность представления

сигнала требует увеличивать fд, а стремление сделать

вычислитель как можно боде простым приводит к желанию понизить f д.

Однако существует ограничение на

минимальное значение fд:

для полного восстановления сигнала по его отсчетам x(nТ) нужно, чтобы частота дискретизации fд была, как минимум, в два раза больше

наивысшей частоты Fв в

спектре передаваемого сигнала x(t).

fд ≥ 2Fв; Т

≤

Отсюда следует, что при

бесконечном спектре, когда F → ∞, дискретизация невозможна.

Тем не менее, в спектре любого конечного сигнала есть такие высшие

составляющие, которые, начиная с некоторой верхней частоты fв, имеют незначительные амплитуды, и потому

ими можно пренебречь без заметного искажения самого сигнала. Значение fв определяется конкретным

типом сигнала и решаемой задачей. Например: для стандартного телефонного

сигнала fв = 3,4 кГц,

минимальная стандартная частота его дискретизации fд = 8 кГц. Ограничение спектра до

Ограничение спектра до

частоты F = fв осуществляется фильтром

нижних частот ФНЧ.

Квантование отсчетов по уровням (квантование)

– производится с целью формирования

последовательности чисел: весь диапазон изменения величины отсчетов разбивается

на некоторое количество дискретных уровней, и каждому отсчету по определенному

правилу присваивается значение одного из двух ближайших уровней квантования,

между которыми оказывается данный отсчет. В результате получается последовательность

чисел x(nТ) = x(n), представляемых в двоичном коде. Количество уровней

определяется разрядностью АЦП. Например: Если разрядность АЦП = 3, то всего

можно иметь к = 23 = 8 уровней квантования, а минимальное значение

отсчета равно 0 (000), а максимальное значение отсчета равно 7 (111). Ясно, что

квантованный отсчет отличается от выборки x(nТ).

Это отличие выражается ошибкой квантования:

,

которая тем больше, чем меньше разрядность АЦП.

После АЦП

последовательность x(nТ) = x(n) поступает на сигнальный процессор (СП), который по заданному

алгоритму каждому отсчету x(n) ставит в однозначное

соответствие выходной отсчет y(nТ) = y(n).

Количество

операций (умножений, сложений и т.д.) для получения одного отсчета может

исчисляться тысячами, поэтому сигнальный процессор должен работать на более высокой

частоте Fг, чтобы успеть

произвести все необходимые действия до поступления очередного отсчета x(n), то есть какой бы сложности не был

алгоритм, время переработки tпер

не должно превышать периода дискретизации T:

tпер ≤ T

Но это может быть обеспечено лишь

в случае, когда тактовая частота fT вычислителя существенно

превышает частоту дискретизации fд:

fд << fT

Именно при этих условиях возможна

работа вычислителя в реальном времени, то есть в темпе поступления входных

отсчетов.

Полученные выходные отсчеты с

сигнального процессора подаются на ЦАП, а затем на сглаживающий фильтр нижних

частот, который преобразует их в аналоговый непрерывный сигнал y(t).

Основные задачи (алгоритмы) сигнальных процессоров:

1) Цифровая фильтрация

Цифровая фильтрация – это селекция по частоте, то есть какие

то частоты пропускать, а какие то нет. За цифровой фильтрацией стоит Z-преобразование, свертка.

2) Спектроскопи

Спектроскопия – это совокупность

методов обработки цифровых сигналов, которые позволяют в сигнале найти все

частотные составляющие сигнала — не выделяя и не искажая их. Здесь производится

ДПФ (дискретное преобразование Фурье) и БПФ (быстрое преобразование Фурье).

3) Идентификация

сигналов

Идентификация сигналов – это

выделение сигналов на фоне частот и помех для того, чтобы удостовериться, что

это сигнал, а не помеха. Здесь производится корреляционный анализ.

Здесь производится корреляционный анализ.

Корреляция – это степень совпадения двух функций.

4) Модуляция и

демодуляция.

За модуляцией и демодуляцией стоит аппаратное,

математическое преобразование Гильберта.

Пример: демодуляция однополосного

сигнала, который получается выделением одной из боковых полос

амплитудно-модулированного сигнала. Результатом демодуляции является

низкочастотный сигнал, представляющий собой огибающую

узкополосного сигнала. Демодулированный сигнал x(n) можно представить в комплексном виде:

|

;

;

,

|

где — мнимый сигнал;

x(n) – вещественный сигнал;

s(n) – огибающая сигнала x(n).

|

Из формул видно,

что x(n) инаходятся в квадратуре относительно друг друга, то

есть их фазы отличаются на π/2. Следовательно, необходимо иметь

Следовательно, необходимо иметь

фазовращатель на π/2. Такие сигналы называются сопряженными по Гильберту, а устройство,

формирующее пару сопряженных сигналов, называется цифровым преобразователем

Гильберта (ЦПГ), который позволяет организовать вычисление огибающей s(n) сигнала x(n).

5) Сжатие, растяжение,

перенос спектра

За сжатием, растяжением, переносом спектра стоит то же самое

преобразование Гильберта. Считаются одним из модификаций модуляции и демодуляции.

Вычисления алгоритмов цифровой

обработки сигналов сводятся к виду в реальном масштабе времени, когда

время выполнения операций полностью прогнозируемо:

|

,

|

где n

x(n) – отсчеты

y(n) – отсчеты реакции;

bк — вещественные коэффициенты, полностью

x(n-к) — отсчеты

|

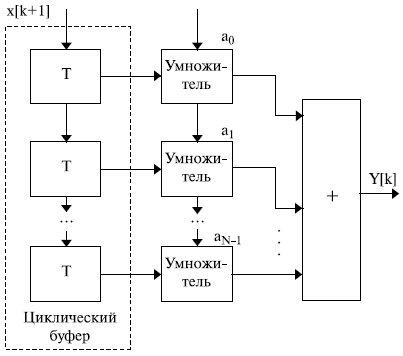

Фильтр,

описываемый данным выражением, называется нерекурсивным, или КИХ-фильтром (фильтром

с конечной импульсной характеристикой).

Пример: Нужно сделать дискретизацию за определенное время, а

не вообще. Пусть частота дискретизации fд = 48 кГц (округлим до 50 кГц). Нужно сделать дискретизацию за

20 мкс. Возьмем N = 5 и

распишем формулу:

y0

= b0x(0 — 0) + b1x(0 — 1) + b2x(0— 2) + b3x (0 — 3) + b4x(0 — 4)

= b0x0 + b1x — 1 + b2x

— 2 + b3x — 3 + b4x – 4

y1

= b0x(1 — 0) + b1x(1 — 1) + b2x(1— 2) + b3x (1 — 3) + b4x(1 — 4)

= b0x1 + b1x 0 + b2x

— 1 + b3x — 2 + b4x – 3

y2

= b0x(2 — 0) + b1x(2 — 1) + b2x(2— 2) + b3x (2 — 3) + b4x(2 — 4)

= b0x2 + b1x 1 + b2x

0 + b3x — 1 + b4x – 2

y3 =

b0x(3 — 0) + b1x(3 — 1) + b2x(3— 2) + b3x (3 — 3) + b4x(3 — 4)

= b0x3 + b1x 2 + b2x

1+ b3x 0 + b4x – 1

y4

= b0x(4 — 0) + b1x(4 — 1) + b2x(4— 2) + b3x (4 — 3) + b4x(4 — 4)

= b0x4 + b1x 3 + b2x

2 + b3x 1 + b4x 0

y5

= записывается как y0.

Примечание: x0 – это отсчет показания АЦП в данный момент времени.

Если отсчет показания АЦП с отрицательным знаком, то это означает, что отсчет –

предшествующий. Для вычисления y0

нужно использовать текущее показание АЦП и четыре предшествующих ему

показаний, а для вычисления y1

нужно использовать x1

и четыре предшествующих ему показаний и т.д.

2. Структура процессоров цифровой

обработки сигналов

Базовой операцией цифровой обработки

сигналов является операция умножения и добавление (накопление) результата

умножения. Устройство комбинированного сложения и умножения часто обозначают

при описаниях мнемоникой МАС (Multiplier-Adder

Combination). Для того чтобы работать

с высокой производительностью, процессор должен выполнять операцию МАС за один

цикл (такт) работы процессора. Это должно выполняться аппаратно, а не

Это должно выполняться аппаратно, а не

программно. Отсчеты сигнала, коэффициенты фильтра и команды программы хранятся

в памяти. Для выполнения операции требуется произвести три выборки из памяти –

команды и двух сомножителей. Следовательно, для работы с высокой

производительностью эти три выборки необходимо произвести за один такт работы

процессора. При этом подразумевается, что результат операции остается в устройстве

выполнения операции (в центральном процессорном устройстве), а не помещается в

память. В более общем случае, нужна еще операция записи результата в память,

т.е. необходимы четыре обращения к памяти за цикл. Таким образом, производительность

процессора, прежде всего, определяется возможностями обмена данными между

центральным процессорным устройством и памятью процессора и организацией их

взаимодействия.

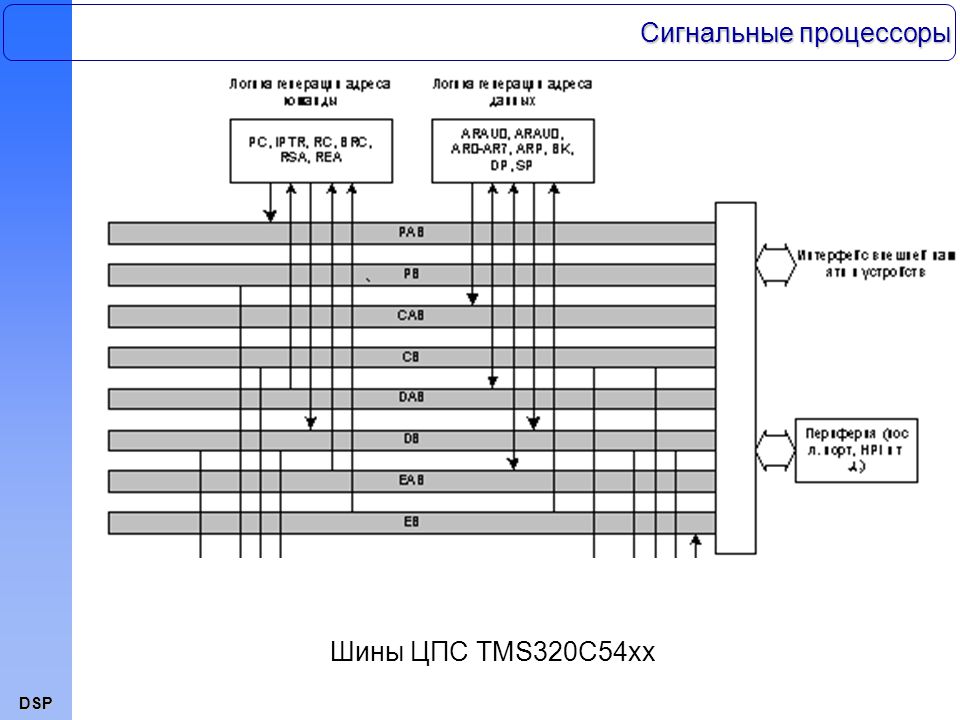

В процессорах цифровой

обработки сигналов должна быть гарвардская

архитектура с раздельными шинами данных и команд. Благодаря этому, можно

Благодаря этому, можно

будет одновременно производить операции обращения к различным устройствам

памяти, т.е. синхронно выбирать команду из памяти программ и сомножитель из

памяти данных. Память данных должна состоять из двух частей (традиционно они

называются: памятью x и

памятью y). Для

хранения отсчетов сигнала используется, например, память x, а для хранения коэффициентов – память

y.

Таким образом, в процессорах Motorola для того, чтобы можно было произвести две выборки операндов

за один такт, увеличивается количество независимых модулей памяти и количество

шин для передачи данных. Процессоры имеют три банка (модуля) памяти для трех

выборок за один такт и соответствующее количество шин. Проблемы с

быстродействием могут возникнуть в случае нехватки внутренней памяти. По

внешним шинам можно осуществить только одно обращение к памяти за такт.

В цифровых

процессорах обработки сигналов используют специализированные устройства генерации адреса (УГА),

которые формируют адреса данных, извлекаемых из памяти данных. УГА функционируют

УГА функционируют

параллельно с другими модулями и позволяют одновременно с выполнением операций

в АЛУ вычислять адреса операндов для следующей команды.

Циклические

процессы, т.е. повторение одиночных команд и их блоков, занимают значительное место

среди алгоритмов цифровой обработки сигналов. Обычная организация циклов

программным образом требует использования команд формирования и проверки условий

окончания циклов, которые должны выполняться при каждом прохождении «тела» цикла.

На выполнение этих команд затрагивается время. Поэтому должен быть аппаратный счетчик циклов. В ПЦОС

используются устройства, которые позволяют организовать циклы с «нулевыми

потерями» времени на организацию (проверку условий окончания).

В процессорах Motorola используется команда цикла DO, которая работает с регистрами

начала и конца цикла (LC

и LA).

Гарвардская архитектура автоматически

открывает многоступенчатый конвейер (от 3 до 11 ступеней конвейера). В базовом

В базовом

варианте: три ступени конвейера.

Базовый

вариант: Motorola DSP56000 = 560

= 56К, где К = 000

Номер Процессор

серии в этой серии

3. Основные

показатели процессоров цифровой обработки сигналов

1. )

)

Способ представления данных.

По этому показателю все процессоры

цифровой обработки сигналов делятся на:

1.1. Процессоры

с фиксированной запятой (ФЗ) или процессоры с фиксированной точкой (ФТ).

1.2. Процессоры

с плавающей запятой (ПЗ) или процессоры с плавающей точкой (ПТ).

Наиболее распространены процессоры с

фиксированной запятой или процессоры с фиксированной точкой — они стоят во всех телефонах.

В

процессорах с плавающей запятой данные представляются в виде мантиссы или порядка.

Процессоры с плавающей запятой значительно более сложные и наиболее дорогие (в

несколько сотен долларов).

2.) Разрядность

представления данных.

Для процессоров с фиксированной точкой

разрядность равна 16 (у большинства сигнальных процессоров) или равна 24 (у

фирмы Motorola).

Для процессоров с плавающей точкой

разрядность равна 32 (из них порядок представляется 8 разрядами, мантисса 23 разрядами, а знак 1

разрядом).

У процессоров с плавающей точкой

большой диапазон представления чисел (мантиссу откидываем) с учетом знака: от 2

−128 до 2127.

Диапазон представления чисел

устанавливает границы между минимально и максимально допустимыми значениями,

представляемыми в заданном формате и коде.

Динамический

диапазон (ДД):

ДД

= |max значение|

/ |min значение

≠

0|

Динамический

диапазон в децибелах равен:

20 lg (ДД) = 20 lg (|max значение| / |min значение ≠ 0|)

Динамический диапазон сигналов, с

которыми могут без искажений работать процессоры, у процессоров с фиксированной

точкой значительно уже (на несколько десятичных порядков). При относительно

простых алгоритмах обработки это может быть неважно, т. к. динамический диапазон

к. динамический диапазон

реальных входных сигналов чаще всего меньше, чем допускает DSP, однако в

некоторых случаях возможно возникновение ошибок переполнения при выполнении

программы. Это приводит к принципиально неустранимым нелинейным искажениям выходного

сигнала, аналогичным искажениям из-за ограничения в аналоговых схемах.

3) Производительность

Одна из самых частых

ошибок разработчика — отождествление тактовой частоты и быстродействия, что в

большинстве случаев неправильно. Очень часто скорость работы DSP указывают в

MIPS (миллионах инструкций в секунду). Это наиболее просто измеряемый параметр.

Производительность нормальных процессоров – это несколько десятков MIPS.

Однако

проблема сравнения скорости различных DSP состоит в том, что процессоры

имеют различные системы команд, и для

выполнения одного и того же алгоритма разными процессорами требуется разное

число этих команд. Кроме того, иногда для выполнения различных команд одним

Кроме того, иногда для выполнения различных команд одним

процессором требуется различное количество тактов синхронизации. В результате

процессор со скоростью 1000 MIPS вполне может оказаться в разы медленнее процессора

со скоростью 300 MIPS, особенно при различной их разрядности.

Одно из

решений этой проблемы — сравнивать процессоры по скорости выполнения

определенных операций, например, операции умножения с

накоплением (MAC). Скорость

выполнения таких операций критична для алгоритмов,

использующих цифровую

фильтрацию, корреляцию и преобразования Фурье. К сожалению,

такая оценка также не

дает полной информации о реальном быстродействии процессора.

Наиболее

точной является оценка скорости исполнения определенных алгоритмов —

например, КИХ и БИХ — фильтрации, однако это требует разработки

соответствующих программ и тщательного анализа результатов тестирования.

Существуют компании, занимающиеся анализом и сравнением

процессоров по основным характеристикам, в том числе и по скорости. Лидером

Лидером

среди таких компаний является BDTI (Berkeley

Design Technology, Inc).

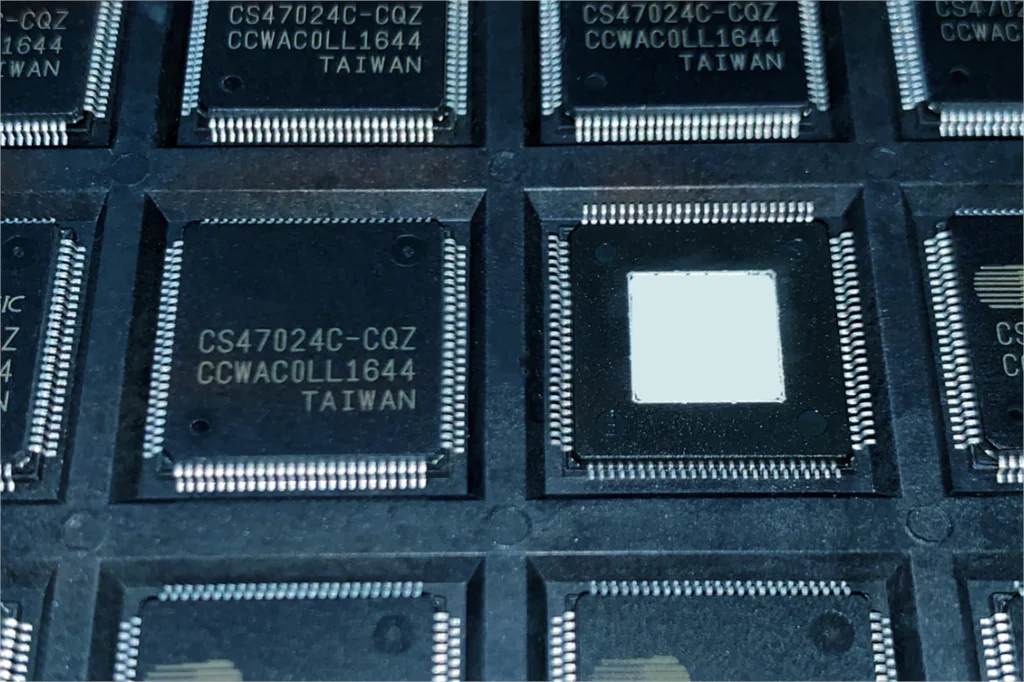

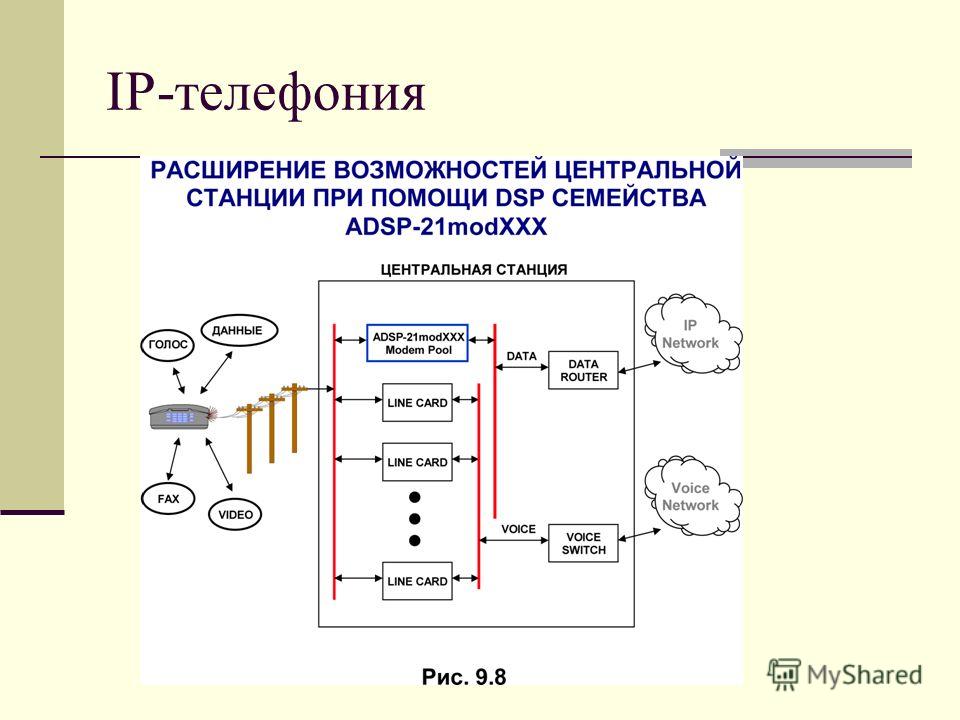

4. Основные

производители сигнальных процессоров

1.) Фирма Texas Instruments (TI) занимает около 48 % рынка ПЦОС. Именно

она выпустила в 1982 г. первый ПЦОС, который имел коммерческий

успех. ПЦОС TMS32010 использовался в игре Speak and Spell («Скажи и

произнеси по буквам»), а также в говорящей кукле по имени Джули. Все

процессоры цифровой обработки сигналов фирмы Texas Instruments идут под маркой:

TMS3200xxx.

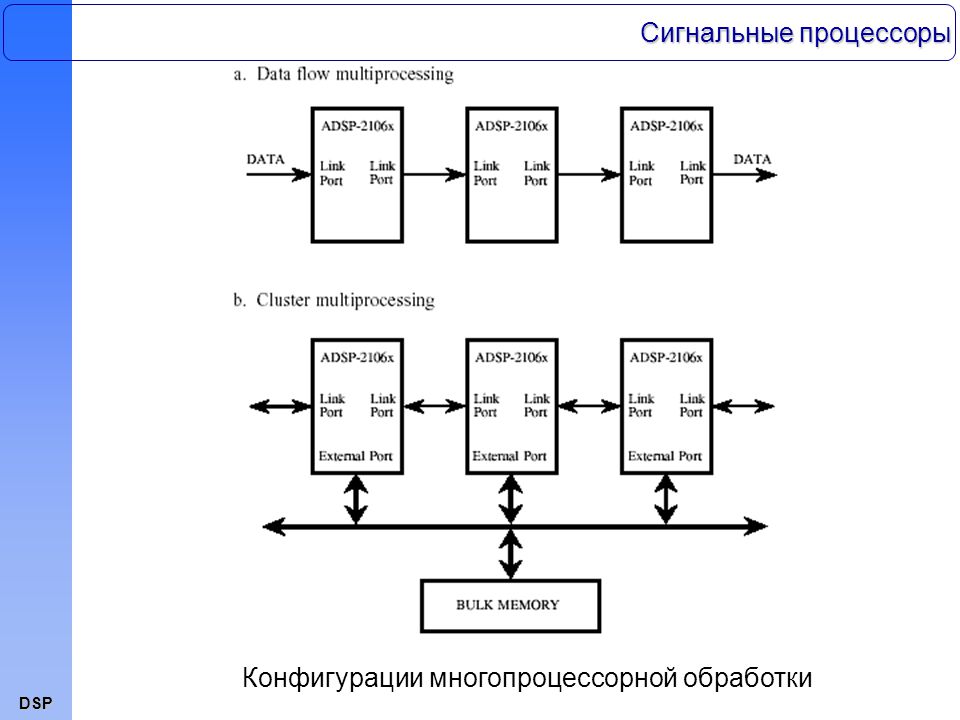

2.) Фирма Analog Devices (AD). Все

процессоры цифровой обработки сигналов фирмы Analog Devices идут под маркой: ADSP21xxx.

3.) Фирма Motorola. Серии: DSP560xx

DSP561xx

Процессоры с фиксированной точкой.

DSP563xx

DSP566xx

DSP568xx

Фирма

Intel раньше

тоже входила в первую тройку производителей сигнальных процессоров, но сейчас

её оттеснили.

В нашей

стране также производятся сигнальные процессоры, правда они несколько уступают

зарубежным аналогам, но они есть. Например: в настоящее время научно-исследовательский

институт электронной техники («НИИЭТ») серийно выпускает 16-разрядные

процессоры ЦОС с фиксированной запятой М1867ВМx

с производительностью 5 MIPS.

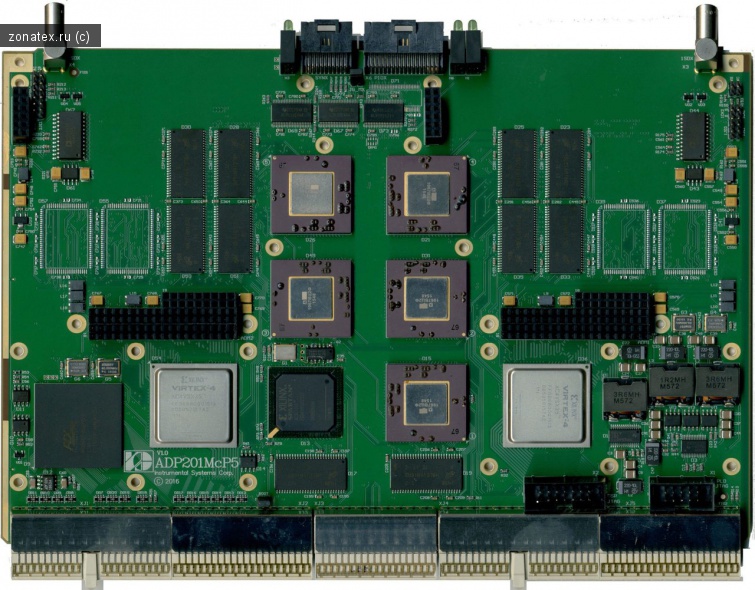

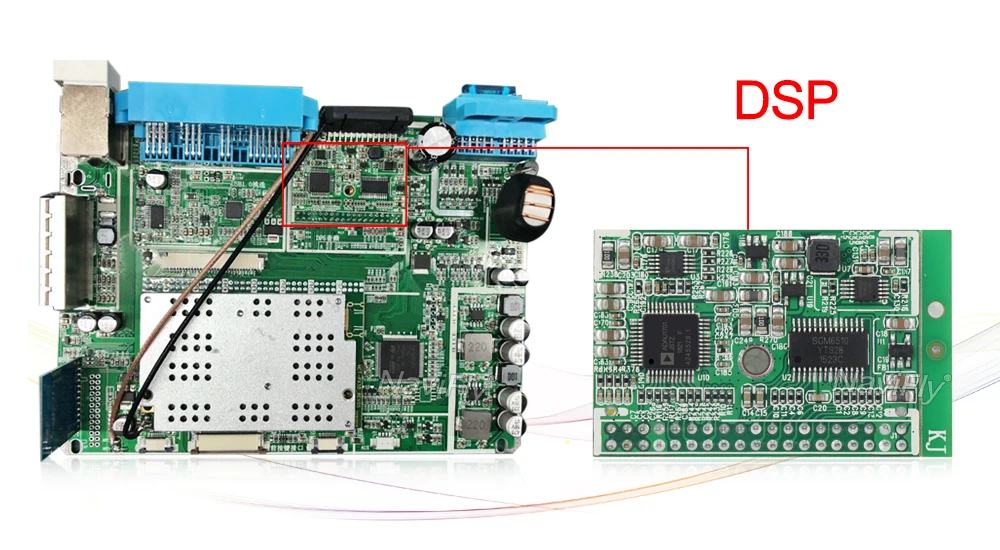

5. Аппаратная реализация

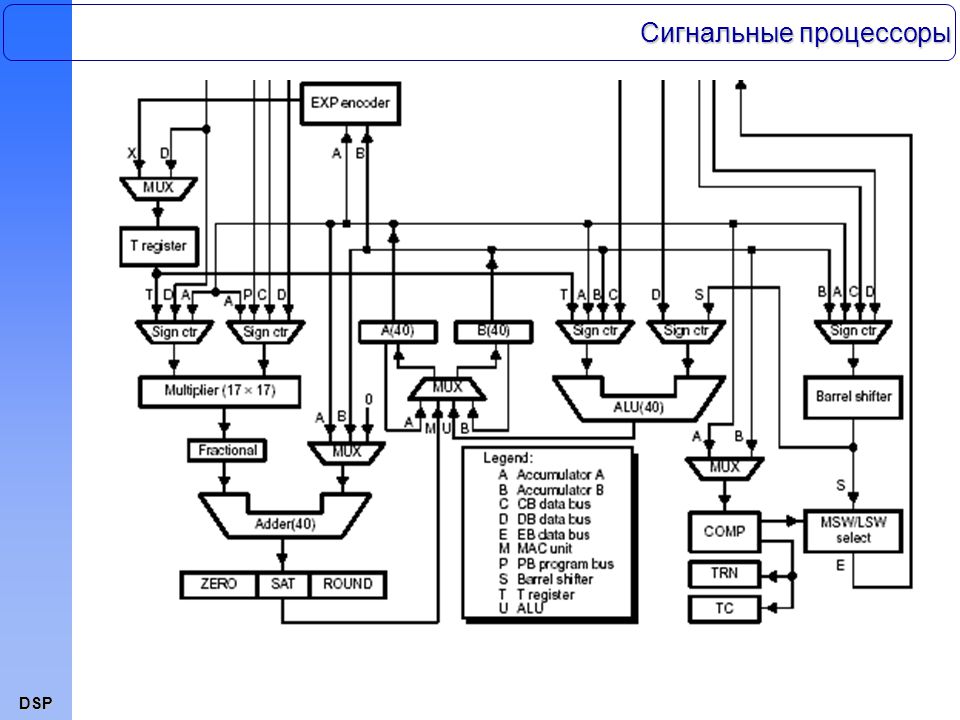

Процессор цифровой обработки сигналов разбивается на две

части: операционный блок и блок управления.

Операционный блок

Блок управления операцией.

На

входные регистры x0, x1,y0, y1 из памяти поступают

данные и передаются на МАС или АЛУ, которые могут использоваться как отдельно,

так и в паре. Если нужно использовать данные двойной длины, то, как правило, используют

Если нужно использовать данные двойной длины, то, как правило, используют

16 разрядов. Результат выполнения операции из аккумулятора А или В передаётся в

память данных через сдвигатель — выходной.

Распределение

нагрузки между МАС и АЛУ: 62 команды в базовом варианте, из них: 61 — АЛУ и 1 -

МАС.

МАС

выполняется в 1000 раз чаще, чем все другие команды и, именно он определяет скорость

быстродействия.

Рис. Схема блока МАС

В блоке МАС

после умножения первое суммирование происходит с нулём, а далее после каждого умножения

происходит суммирование с каждым значением аккумулятора. Аккумуляторов всегда

два или более.

Сдвигатель

позволяет производить сдвиги при передаче и загрузке операндов без использования

дополнительных команд.

Если в

процессорах фирмы Motorola (в базовом варианте Motorola DSP560xx) разрядность слова равна 24, то длина расширенного слова

составляет: 24 + 24 + 8 = 56 битов, где 8 разрядов отводится на расширение

данных.

Если в

процессорах фирмы Motorola разрядность слова равна 16, то длина расширенного

слова составляет: 16 + 16 + 8 = 40 битов, где 8 разрядов отводится на

расширение данных.

Пример представления целых чисел в форматах двойное и расширенное слово

аккумулятора длиной 56 битов в процессорах DSP560xx фирмы Motorola:

Примечание:

На рисунке расширение EXT заполнено нулями – значением 47-го знакового бита.

Представление целых чисел в формате с ФТ в форматах двойное и расширенное слово

предполагает следующее функциональное распределение битов:

1) Старший бит MSB старшего слова MSP используется:

–

как знаковый

при представлении целых чисел со знаком;

значение MSB = 0 соответствует положительному знаку, а MSB = 1 -

отрицательному знаку; ноль считается положительным; остальные биты являются

значащими;

–

как старший значащий при представлении беззнаковых чисел; беззнаковыми называются

целые числа, имеющие положительный знак по умолчанию.

2) Все биты, кроме знакового, считаются значащими; они выравниваются по правому

краю формата, т.е. младший бит LSB соответствует младшему разряду целого двоичного числа.

3) При представлении целых

чисел со знаком в формате «расширенное слово» в расширении EXT происходит расширение знака; это означает, что все

биты EXT автоматически заполняются значением старшего знакового бита MSB слова MSP:LSP.

4) При представлении целых беззнаковых чисел в формате

«расширенное слово» все биты EXT

обнуляются.

Руководство для ученых и инженеров по цифровой обработке сигналов, 1999 г. | Образование

Образование

Образовательная библиотека

- Руководство по цифровой обработке сигналов

Включить JavaScript

Руководство для ученых и инженеров по цифровой обработке сигналов, Стивен В. Смит, второе издание, California Technical Publishing, 1999, ISBN 0-9660176-7-6, ISBN 0-9660176-4-1, ISBN 0-9660176-6- 8.

Смит, второе издание, California Technical Publishing, 1999, ISBN 0-9660176-7-6, ISBN 0-9660176-4-1, ISBN 0-9660176-6- 8.

Эта книга представляет собой практическое введение в цифровую обработку сигналов. Охватывая широкий спектр тем, включая линейные системы, дискретные преобразования Фурье, быстрые преобразования Фурье, цифровые фильтры, эта книга является идеальным вводным текстом для тех, кто плохо знаком с DSP, и отличным справочником для более опытных пользователей.

Книга «Руководство для ученых и инженеров по цифровой обработке сигналов» доступна для скачивания:

Вы можете скачать книгу полностью здесь в формате zip, «Руководство для ученых и инженеров по цифровой обработке сигналов» (zip) или по главам ниже.

- Фундаменты

- Основы

- Цифровые фильтры

- Приложения

- Комплексные методы

Содержание (pdf)

Фундаменты

- Глава 1: Широта и глубина DSP (pdf)

- Глава 2: Статистика, вероятность и шум (pdf)

- Глава 3: АЦП и ЦАП (pdf)

- Глава 4: Программное обеспечение DSP (pdf)

Основы

- Глава 5: Линейные системы (pdf)

- Глава 6.

Свертка (pdf)

Свертка (pdf) - Глава 7: Свойства свертки (pdf)

- Глава 8. Дискретное преобразование Фурье (pdf)

- Глава 9: Применение ДПФ (pdf)

- Глава 10. Свойства преобразования Фурье (pdf)

- Глава 11. Пары преобразования Фурье (pdf)

- Глава 12. Быстрое преобразование Фурье (pdf)

- Глава 13. Непрерывная обработка сигналов (pdf)

Цифровые фильтры

- Глава 14: Знакомство с цифровыми фильтрами (pdf)

- Глава 15. Фильтры скользящего среднего (pdf)

- Глава 16. Фильтры Windowed-Sinc (pdf)

- Глава 17. Пользовательские фильтры (pdf)

- Глава 18. Свертка БПФ (pdf)

- Глава 19. Рекурсивные фильтры (pdf)

- Глава 20. Фильтры Чебышева (pdf)

- Глава 21. Сравнение фильтров (pdf)

Приложения

- Глава 22. Обработка аудио (pdf)

- Глава 23. Формирование и отображение изображений (pdf)

- Глава 24.

Линейная обработка изображений (pdf)

Линейная обработка изображений (pdf) - Глава 25. Специальные методы визуализации (pdf)

- Глава 26. Нейронные сети (и не только!) (pdf)

- Глава 27. Сжатие данных (pdf)

- Глава 28: Цифровые сигнальные процессоры (pdf)

- Глава 29. Начало работы с DSP (pdf)

Комплексные методы

- Глава 30: Комплексные числа (pdf)

- Глава 31. Комплексное преобразование Фурье (pdf)

- Глава 32. Преобразование Лапласа (pdf)

- Глава 33. Z-преобразование (pdf)

Глоссарий (pdf)

Алфавитный указатель (pdf)

Цифровая обработка сигналов с фиксированной точкой и с плавающей запятой

Обзор технологии и рекомендации по применению

Инновации начинаются с цифровой обработки сигналов

Цифровые сигнальные процессоры (DSP) необходимы для обработки в режиме реального времени оцифрованных данных реального мира, выполняя высокоскоростные числовые вычисления, необходимые для широкого спектра приложений — от базовой бытовой электроники до сложных промышленных приборов. Программное обеспечение, программируемое для максимальной гибкости и поддерживаемое простыми в использовании и недорогими инструментами разработки, DSP позволяет разработчикам встраивать в свои продукты инновационные функции и отличать их ценность, а также быстро и с минимальными затратами выводить эти продукты на рынок.

Программное обеспечение, программируемое для максимальной гибкости и поддерживаемое простыми в использовании и недорогими инструментами разработки, DSP позволяет разработчикам встраивать в свои продукты инновационные функции и отличать их ценность, а также быстро и с минимальными затратами выводить эти продукты на рынок.

Разработчики систем учитывают множество соображений при выборе цифровых сигнальных процессоров для своих приложений. Среди ключевых факторов, которые следует учитывать, — вычислительные возможности, необходимые для приложения, стоимость процессора и системы, характеристики производительности и простота разработки. Сбалансировав эти факторы вместе, разработчики могут определить DSP, который лучше всего подходит для приложения.

Фиксированная точка и плавающая точка

Цифровую обработку сигналов можно разделить на две категории — с фиксированной точкой и с плавающей запятой. Эти обозначения относятся к формату, используемому для хранения и обработки числовых представлений данных. DSP с фиксированной запятой предназначены для представления и обработки целых чисел — положительных и отрицательных целых чисел — с помощью как минимум 16 бит, что дает до 65 536 возможных битовых комбинаций (2 16 ). DSP с плавающей запятой представляют рациональные числа и манипулируют ими с помощью как минимум 32 битов способом, аналогичным экспоненциальному обозначению, где число представлено мантиссом и показателем степени (например, A x 2 B , где «A» — это мантисса и «B» — показатель степени), что дает до 4 294 967 296 возможных битовых комбинаций (2 32 ).

DSP с фиксированной запятой предназначены для представления и обработки целых чисел — положительных и отрицательных целых чисел — с помощью как минимум 16 бит, что дает до 65 536 возможных битовых комбинаций (2 16 ). DSP с плавающей запятой представляют рациональные числа и манипулируют ими с помощью как минимум 32 битов способом, аналогичным экспоненциальному обозначению, где число представлено мантиссом и показателем степени (например, A x 2 B , где «A» — это мантисса и «B» — показатель степени), что дает до 4 294 967 296 возможных битовых комбинаций (2 32 ).

Термин «фиксированная точка» относится к соответствующему способу представления чисел с фиксированным количеством цифр после, а иногда и до десятичной точки. При представлении с плавающей запятой размещение десятичной точки может «плавать» относительно значащих цифр числа. Например, представление с фиксированной запятой с единым соглашением о размещении десятичной точки может представлять числа 123,45, 1234,56, 12345,67 и т. д., тогда как представление с плавающей запятой может дополнительно представлять 1,234567, 123456,7, 0,00001234567, 1234567000000000 и т. д. Таким образом, с плавающей запятой может поддерживать гораздо более широкий диапазон значений, чем с фиксированной запятой, с возможностью представления очень маленьких чисел и очень больших чисел.

д., тогда как представление с плавающей запятой может дополнительно представлять 1,234567, 123456,7, 0,00001234567, 1234567000000000 и т. д. Таким образом, с плавающей запятой может поддерживать гораздо более широкий диапазон значений, чем с фиксированной запятой, с возможностью представления очень маленьких чисел и очень больших чисел.

В записи с фиксированной запятой промежутки между соседними числами всегда равны единице, тогда как в записи с плавающей запятой промежутки между соседними числами расположены неравномерно — промежуток между любыми двумя числами примерно в десять миллионов раз меньше значения числа (стандартный формат ANSI/IEEE Std. 754) с большими промежутками между большими числами и небольшими промежутками между маленькими числами.

Динамический диапазон и точность

Возведение в степень, присущее вычислениям с плавающей запятой, обеспечивает гораздо больший динамический диапазон — самые большие и самые маленькие числа, которые могут быть представлены, — что особенно важно при обработке очень больших наборов данных или наборов данных, где диапазон может быть непредсказуемым. Таким образом, процессоры с плавающей запятой идеально подходят для приложений с интенсивными вычислениями.

Таким образом, процессоры с плавающей запятой идеально подходят для приложений с интенсивными вычислениями.

Также важно учитывать форматы с фиксированной и плавающей запятой в контексте точности — размера промежутков между числами. Каждый раз, когда DSP генерирует новое число с помощью математических вычислений, это число должно быть округлено до ближайшего значения, которое может быть сохранено в используемом формате. Округление и/или усечение чисел во время обработки сигнала естественным образом приводит к ошибке квантования или «шуму» — отклонению между фактическими аналоговыми значениями и квантованными цифровыми значениями. Поскольку промежутки между соседними числами могут быть намного больше при обработке с фиксированной запятой по сравнению с обработкой с плавающей запятой, ошибка округления может быть гораздо более выраженной. Таким образом, обработка с плавающей запятой обеспечивает гораздо большую точность, чем обработка с фиксированной запятой, что делает процессоры с плавающей запятой идеальным DSP, когда точность вычислений является критическим требованием.

Ключевые аспекты — затраты, простота разработки и производительность

Соображения динамического диапазона и точности обычно определяют критерии, используемые разработчиками, чтобы определить, какие процессоры с фиксированной или с плавающей запятой идеально подходят для приложения — там, где требования к вычислениям высоки, предпочтение отдается плавающей запятой. Но есть много других важных взаимосвязанных факторов, которые следует учитывать при выборе между двумя форматами.

Стоимость процессора : Способность проектировщика снизить стоимость спецификации (BOM) для продукта оказывает прямое влияние на конкурентоспособные цены, проникновение на рынок и прибыльность. DSP с фиксированной запятой используются в большем количестве приложений с большим объемом, чем DSP с плавающей запятой, и поэтому обычно дешевле, чем DSP с плавающей запятой, из-за масштаба производства. Переменные системы на кристалле (SOC), включая встроенную память, встроенные периферийные устройства для конкретных приложений и возможности подключения, также могут влиять на стоимость и функциональность процессоров как с фиксированной, так и с плавающей запятой.

Простота разработки : Чем проще разработчику разработать продукт, тем больше вероятность того, что этот продукт будет выпущен на рынок раньше конкурентов. Как правило, проще разрабатывать алгоритмы для DSP с плавающей запятой, поскольку алгоритмы с фиксированной запятой требуют больших манипуляций для компенсации шума квантования. Таким образом, разработчики обычно выбирают DSP с плавающей запятой при реализации сложных алгоритмов. Здесь снова переменные SOC могут сократить циклы разработки продуктов, как и экосистема связанных инструментов разработки продуктов и стороннего программного обеспечения поддержки.

Производительность : Скорость, с которой DSP выполняет операции в приложении, имеет решающее значение. Разработчики должны реализовать формат DSP, который будет обрабатывать алгоритмы с наибольшей эффективностью. Хотя можно запрограммировать код с фиксированной запятой для процессора с плавающей запятой и наоборот, могут возникнуть значительные ограничения производительности. Эффективность производительности также может влиять на энергоэффективность. Например, в случае, когда процессор с плавающей запятой реализован для выполнения задач с фиксированной запятой, потребляемая мощность может быть больше, чем если бы был реализован процессор с фиксированной запятой, что может повлиять на требования к источнику питания и охлаждению. , а также связанные с этим затраты на спецификации.

Эффективность производительности также может влиять на энергоэффективность. Например, в случае, когда процессор с плавающей запятой реализован для выполнения задач с фиксированной запятой, потребляемая мощность может быть больше, чем если бы был реализован процессор с фиксированной запятой, что может повлиять на требования к источнику питания и охлаждению. , а также связанные с этим затраты на спецификации.

Таким образом, DSP с плавающей запятой оптимизированы для специализированных приложений с интенсивными вычислениями, тогда как DSP с фиксированной запятой оптимизированы для приложений общего назначения с большими объемами. Затраты на разработку для фиксированной точки могут быть выше из-за относительной сложности реализации алгоритма, но стоимость конечного продукта часто снижается. Стоимость продукта для приложений, использующих DSP с плавающей запятой, может быть выше из-за стоимости процессора и меньших объемов производства, но разработчики осознают преимущества простоты разработки и повышения общей точности системы. В конечном итоге требования к набору данных, связанные с целевым приложением, будут диктовать необходимость обработки с фиксированной или плавающей запятой.

В конечном итоге требования к набору данных, связанные с целевым приложением, будут диктовать необходимость обработки с фиксированной или плавающей запятой.

Analog Devices — лидер отрасли в области инноваций DSP

Обеспечивая исключительную производительность и ценность, а также дополняя богатую экосистему инструментов разработки, приложений и сторонней поддержки, цифровые сигнальные процессоры Analog Devices являются процессорами выбора для широкого спектра инновационных приложений.

ADI Blackfin

® Процессоры цифровых сигналов с фиксированной точкой

16/32-разрядные цифровые сигнальные процессоры Blackfin с фиксированной запятой

компании Analog Devices разработаны специально для удовлетворения вычислительных требований и ограничений по мощности современных встроенных аудио-, видео- и коммуникационных приложений. Процессоры Blackfin обеспечивают непревзойденную производительность и энергоэффективность благодаря модели программирования RISC, сочетающей расширенные функции обработки сигналов с простыми в использовании атрибутами микроконтроллеров общего назначения. Такое сочетание характеристик обработки позволяет процессорам Blackfin одинаково хорошо работать как в приложениях обработки сигналов, так и в приложениях обработки управления, что во многих случаях устраняет необходимость в отдельных разнородных процессорах. Эта возможность значительно упрощает задачи реализации как аппаратного, так и программного обеспечения.

Такое сочетание характеристик обработки позволяет процессорам Blackfin одинаково хорошо работать как в приложениях обработки сигналов, так и в приложениях обработки управления, что во многих случаях устраняет необходимость в отдельных разнородных процессорах. Эта возможность значительно упрощает задачи реализации как аппаратного, так и программного обеспечения.

ADI Sharc

® Процессоры цифровых сигналов с плавающей запятой

32-разрядные цифровые сигнальные процессоры SHARC с плавающей запятой

компании Analog Devices основаны на архитектуре Super Harvard, которая сочетает исключительную производительность ядра и памяти с выдающейся пропускной способностью ввода-вывода. Эта архитектура Super Harvard расширяет первоначальные концепции отдельных шин памяти программ и данных, добавляя процессор ввода-вывода с соответствующими выделенными шинами. Процессоры SHARC не только удовлетворяют потребности самых требовательных к вычислительным ресурсам приложений по обработке сигналов в реальном времени, но и объединяют большие массивы памяти и специализированные периферийные устройства, предназначенные для упрощения разработки продуктов и сокращения времени вывода их на рынок.

п.

п.

Свертка (pdf)

Свертка (pdf) Линейная обработка изображений (pdf)

Линейная обработка изображений (pdf)