Edp матрица что это: Распиновка ходовых LCD матриц LVDS и eDP для ноутбуков

Содержание

Замена матрицы ноутбука TN на IPS, замена, распиновка 30 pin и 40 pin

Ноутбуки стремительно дешевеют, но качество их экранов постоянно падает. Даже на приличные по конфигурации ноутбуки устанавливают дешевые плохие матрицы. Отличить хорошую матрицу от плохой очень просто — отклоните крышку ноутбука и посмотрите под большим углом. Если цвета резко меняются, переходят насыщение, негатив, то это обычная дешевая матрица. Кроме этого у TN матриц черный цвет выглядит неудовлетворительно — с примесью серого. На этой странице рассматривается замена TN матрицы ноутбука на IPS матрицу. Т.е. замена плохой матрицы в ноутбуке на хорошую. Разберем особенности и ограничения возможности замены, как выполнить подбор.

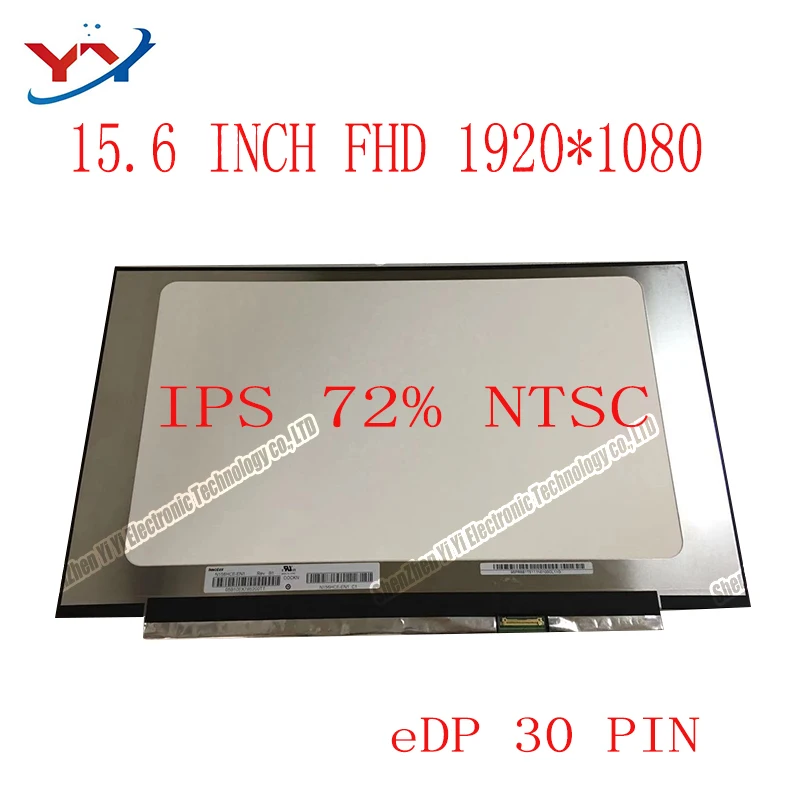

IPS матрицы Full HD

IPS — это торговая марка, принадлежащая LG. Матрицы IPS выгодно отличаются от большинства устанавливаемых массово в ноутбуках матриц своими улучшенными характеристиками. Это широкие углы обзора, особенно по вертикали, хорошая цветопередача, лучшая комфортность для зрения, повышенный контраст. Конечно, матрицы IPS также отличаются по качеству внутри своей группы: 6-битные, с узким охватом цветовой области, более качественные 10-битные с широким охватом. Недостатки IPS матриц — это повышенное энергопотребление, увеличенное время отклика, неоднородность уровня черного.

Конечно, матрицы IPS также отличаются по качеству внутри своей группы: 6-битные, с узким охватом цветовой области, более качественные 10-битные с широким охватом. Недостатки IPS матриц — это повышенное энергопотребление, увеличенное время отклика, неоднородность уровня черного.

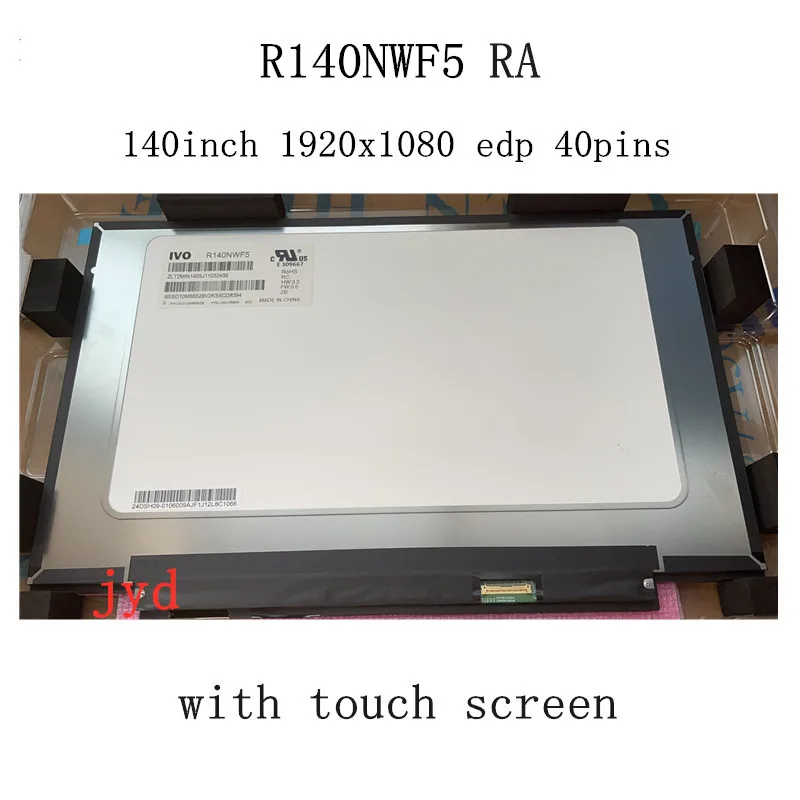

Особенностью матриц IPS для ноутбуков является то, что почти все они имеют разрешение Full HD 1920×1080 и выше.

11.6″ N116HSE-EA1

12.5″ LP125Wh3

15.6″ LP156WF3 SLB1-B2-B3,LP156WF4

17.3″LP173WF3 SLB1-B2-B3

Но есть и IPS матрицы стандартного разрешения 1366×768.

Условия замены матрицы ноутбука на IPS

Во-первых, нужен одинаковый разъем интерфейса — LVDS или eDP. Обычно, матрицу IPS можно установить только в тот ноутбук , где сигнал и шлейф двухканальные (модели которых поддерживают разрешение 1920×1080 10 бит). Никто производить двухканальный кабель для обычных ноутбуков не будет. Практически это означает то, что ноутбука замена матрицы на IPS матрицу можно только в том ноутбуке, у которого есть конфигурация с высоким разрешением.

LVDS шлейфы для матриц ноутбуков отличаются количеством контактов и шин передачи данных. В одноканальных шлейфах для передачи данных используются 4 шины, а в двухканальных 8 шин. Для IPS матриц требуются только двухканальные кабели.

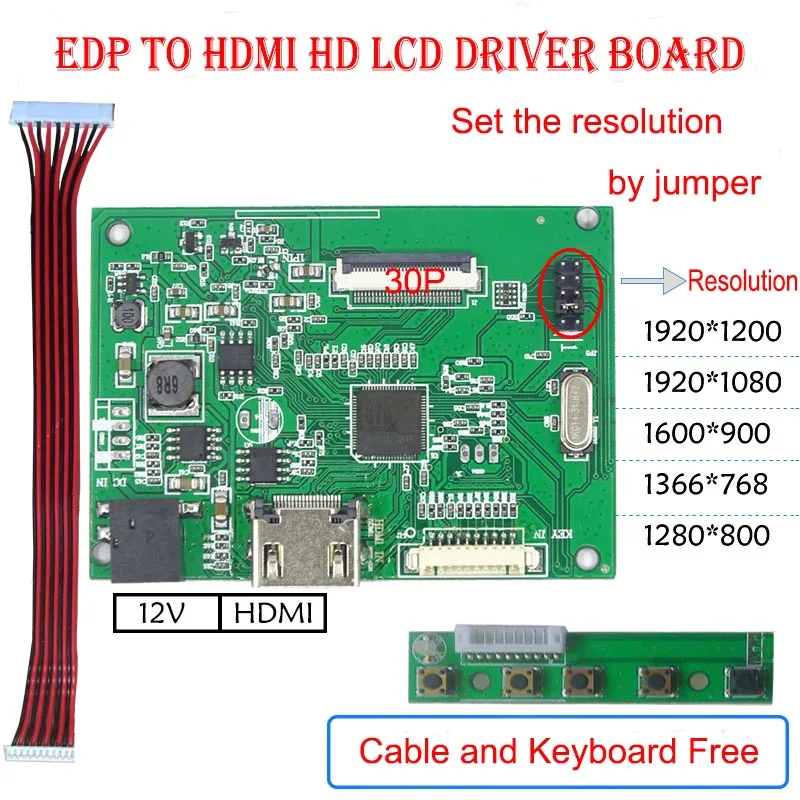

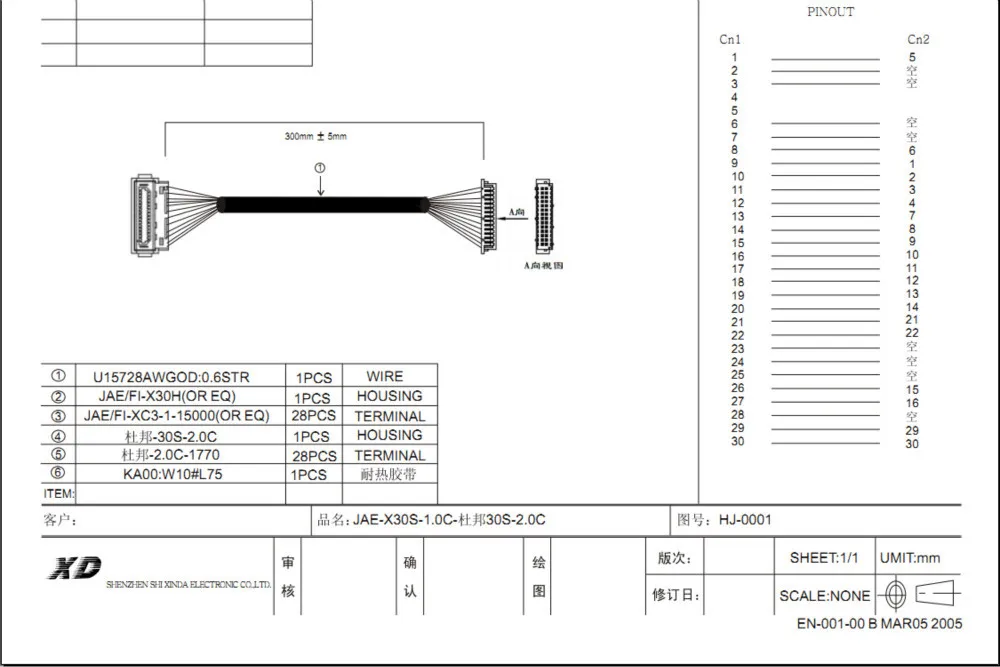

Распиновка кабелей матрицы ноутбука 30 pin LVDS

Таблица распиновки кабелей 30 pin одноканальных и двухканальных LVDS

| Pin | 30 PIN 1 ch LVDS | 30 PIN 2 ch LVDS |

| 1 | Ground | Ground |

| 2 | Pover suppli , 3,3V | Pover supply , 3,3V |

| 3 | Pover suppli , 3,3V | Pover supply , 3,3V |

| 4 | DDS 3V POVER | DDS 3V POVER |

| 5 | Reserved for LCD supplier test point | Reserved for LCD supplier test point |

| 6 | DDC Clock | DDC Clock |

| 7 | DDC Data | DDC Data |

| 8 | — LVDS differential data input, R0 – R5, G0 | — LVDS differential data input, R0 – R5, G0 |

| 9 | + LVDS differential data input, R0 – R5, G0 | + LVDS differential data input, R0 – R5, G0 |

| 10 | Ground | Ground |

| 11 | — LVDS differential data input, G1 – G5, B0 – B1 | — LVDS differential data input, G1 – G5, B0 – B1 |

| 12 | + LVDS differential data input, G1 – G5, B0 – B1 | + LVDS differential data input, G1 – G5, B0 – B1 |

| 13 | Ground | Ground |

| 14 | — LVDS differential data input, B2 – B5, HS/VS/DE | — LVDS differential data input, B2 – B5, HS/VS/DE |

| 15 | + LVDS differential data input, B2 – B5, HS/VS/DE | + LVDS differential data input, B2 – B5, HS/VS/DE |

| 16 | Ground | Ground |

| 17 | — LVDS differential clock input | — LVDS differential clock input |

| 18 | +LVDS differential clock input | +LVDS differential clock input |

| 19 | Ground | Ground |

| 20 | _ | — LVDS differential data input, even pixels, R0 – R5, G0 |

| 21 | _ | + LVDS differential data input, even pixels, R0 – R5, G0 |

| 22 | Ground | Ground |

| 23 | _ | — LVDS differential data input, even pixels, G1 – G5, B0 – B1 |

| 24 | _ | + LVDS differential data input, even pixels, G1 – G5, B0 – B1 |

| 25 | Ground | Ground |

| 26 | _ | — LVDS differential data input, even pixels, B2 – B5, HS/VS/DE |

| 27 | _ | + LVDS differential data input, even pixels, B2 – B5, HS/VS/DE |

| 28 | Ground | Ground |

| 29 | _ | — LVDS differential clock input, even pixels |

| 30 | _ | + LVDS differential clock input, even pixels |

Распиновка кабелей матрицы ноутбука 40 pin LVDS

Таблица распиновки кабелей 40 pin одноканальных и двухканальных

| LDVS 2 ch 40 pin (2-канальный кабель) | LDVS 1 ch 40 pin (1-канальный кабель) | |||

| Pin | Сигнал | Описание | Сигнал | Описание |

| 1 | NC | No Connection | NC | No Connection (Reserve) |

| 2 | VDD | Power Supply +3. 3V 3V | AVDD | PowerSupply 3.3V(typical) |

| 3 | VDD | Power Supply +3.3V | AVDD | PowerSupply 3.3V(typical) |

| 4 | VEDID | EDID +3.3V Power | DVDD | DDC 3.3Vpower |

| 5 | NC | No Connect | NC | No Connection (Reserve) |

| 6 | 6 CLKEDID | EDID Clock Input | SCL | DDCClock |

| 7 | DATAEDID | EDID Data Input | SDA | DDCData |

| 8 | RxOIN0- | -LVDS Differential Data INPUT(Odd R0-R5,G0) | Rin0- | -LVDSdifferential data input(R0-R5,G0) |

| 9 | RxOIN0+ | +LVDS Differential Data INPUT(Odd R0-R5,G0) | Rin0+ | +LVDSdifferential data input(R0-R5,G0) |

| 10 | VSS | Ground | GND | Ground |

| 11 | RxOIN1- | -LVDS Differential Data INPUT(Odd G1-G5,B0-B1) | Rin1- | -LVDSdifferential data input(G1-G5,B0-B1) |

| 12 | RxOIN1+ | +LVDS Differential Data INPUT(Odd G1-G5,B0-B1) | Rin1+ | +LVDSdifferential data input(G1-G5,B0-B1) |

| 13 | VSS Ground | GND | Ground | |

| 14 | RxOIN2- | -LVDS Differential Data INPUT(Odd B2-B5,HS,VS,DE) | Rin2- | -LVDSdifferential data input(B2-B5,HS,VS,DE) |

| 15 | RxOIN2+ | +LVDS Differential Data INPUT(Odd B2-B5,HS,VS,DE) | Rin2+ | +LVDSdifferential data input(B2-B5,HS,VS,DE) |

| 15 | VSS | Ground | GND | Ground |

| 17 | RxOCKIN- | -LVDS Odd Differential Clock INPUT | ClkIN- | -LVDSdifferential clock input |

| 18 | RxOCKIN+ | -LVDS Odd Differential Clock INPUT | ClkIN+ | +LVDSdifferential clock input |

| 19 | VSS | Ground | GND | Ground |

| 20 | RxEIN0- | -LVDS Differential Data INPUT(Even R0-R5,G0) | NC | NC No Connection (Reserve) |

| 21 | RxEIN0- | +LVDS Differential Data INPUT(Even R0-R5,G0) | NC | NC No Connection (Reserve) |

| 22 | VSS | Ground | GND | Ground |

| 23 | RxEIN1- | -LVDS Differential Data INPUT(Even G1-G5,B0-B1) | NC | NC No Connection (Reserve) |

| 24 | RxEIN1+ | +LVDS Differential Data INPUT(Even G1-G5,B0-B1) | NC | NC No Connection (Reserve) |

| 25 | VSS | Ground | GND | Ground–Shield |

| 26 | RxEIN2- | -LVDS Differential Data INPUT(Even B2-B5,HS,VS,DE) | NC | No Connection (Reserve) |

| 27 | RxEIN2+ | NC | No Connection (Reserve) | |

| 28 | VSS | Ground | GND | Ground–Shield |

| 29 | RxECKIN- | ;-LVDS Even Differential Clock INPUT | NC | No Connection (Reserve) |

| 30 | RxECKIN+ | +LVDS Even Differential Clock INPUT | NC | No Connection (Reserve) |

| 31 | VLED_GND | LED Ground | VLED_GND | LED Ground |

| 32 | VLED_GND | LED Ground | VLED_GND | LED Ground |

| 33 | VLED_GND | LED Ground | VLED_GND | LED Ground |

| 34 | NC | No Connection | NC | No Connection (Reserve) |

| 35 | S_PWMIN | System PWM signal Input | PWM System | PWM Signal Input |

| 36 | LED_EN | LED Enable Pin(+3V Input) | 36 LED_EN LED enable pin(+3V Input) | |

| 37 | NC | No Connection | NC | No Connection (Reserve) |

| 38 | VLED LED | Power Supply 7V-21V | VLED | LED Power Supply 7V-20V |

| 39 | VLED LED | Power Supply 7V-21V | VLED | LED Power Supply 7V-20V |

| 40 | VLED LED | Power Supply 7V-21V | VLED | LED Power Supply 7V-20V |

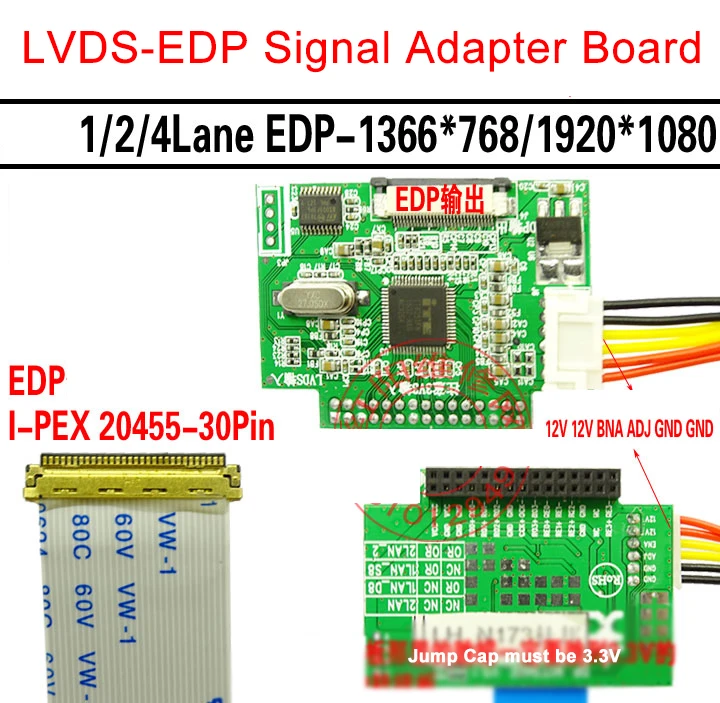

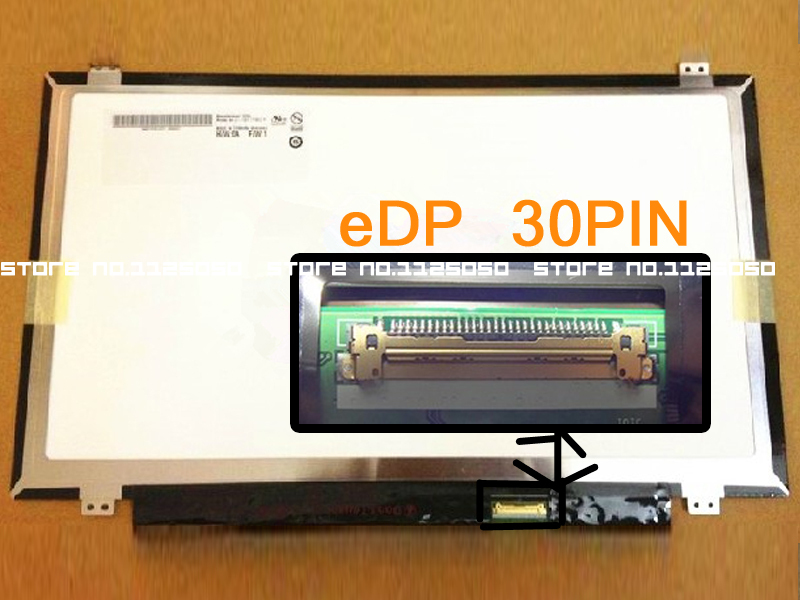

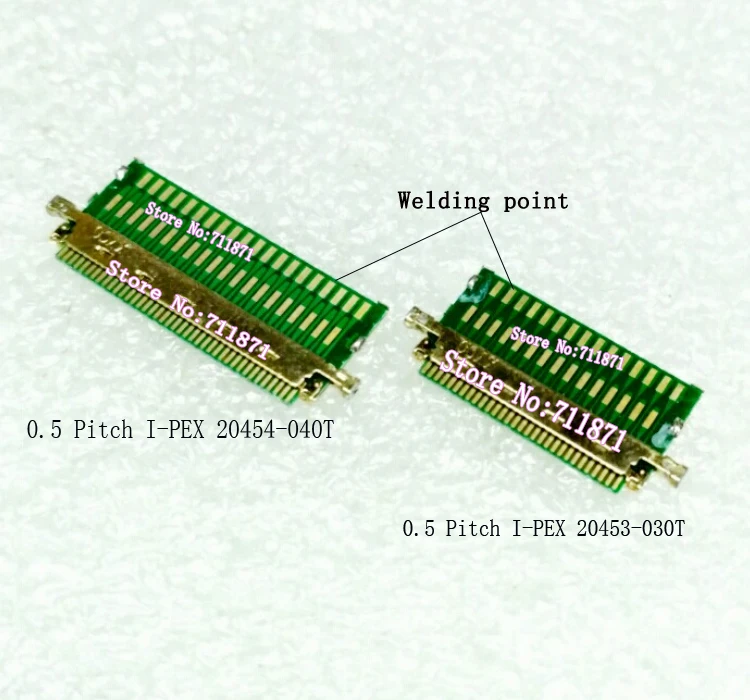

Распиновка стандартной матрицы eDP 30 pin и 40 pin

eDP (Embedded Display Port, встроенный дисплейный порт) — это современный видеопорт, совместимый с DP (DisplayPort).

Распиновка разъема eDP 30 pin

Распиновка разъема eDP 40 pin

IPS матрицы ноутбука с разрешением 1366×768

Однако в последнее время появились матрицы IPS со стандартным разрешением 1366×768, например, LP156WHA(SL)(P1) 30 pin slim, LP156WHA(SL)(A2) 15.6″ 1366×768 slim 40 pin от LG-Philips, N156BGE-EA1 30 pin., LP156WHA(SL)(L1).

К сожалению, матрицы IPS 15.6″ 40 pin с разрешением 1366×768 и стандартной толщины (не slim) LP156WHA(SL)(L1) сейчас перестали производить и завозить в Россию. Поэтому замену стандартной TN матрицы 15.6″ на IPS произвести вряд ли получится, есть шанс только со slim матрицами.

Альтернативы матрицам IPS

Компанией Samsung бала разработана технология PLS матриц в качестве альтернативы матрицам IPS. Наряду с широкими углами обзора, высокой яркостью эти матрицы имеют низкое потребление. Из недостатков — пониженная контрастность, большое время отклика, неравномерность подсветки. Изображение на этих матрицах на порядок лучше у дешевых матриц TN. До появления этих матриц промежуточным вариантом между TN и IPS были матрицы MVA от той же фирмы Samsung.

До появления этих матриц промежуточным вариантом между TN и IPS были матрицы MVA от той же фирмы Samsung.

Сейчас достаточно много производится качественных матриц альтернативной технологии VA (Vertical Alignment) и ее модификации — MVA, PVA, A-NVA, AMVA+

Вторым вариантом замены плохой матрицы TN на улучшенную является подбор матрицы с хорошими характеристиками, например, на матрицу TN B156HW01 V4.

Еще люди ищут:

- Матрицы для ноутбуков Dell

- Матрица для ноутбука HP

- Матрица для ноутбука Lenovo

- Матрицы ноутбуков MSI

Распиновка разъёмов матриц для ноутбуков. 20pin, 30 pin, 40pin, 50pin.

26/08/2018

19.4 K

20pin, 30pin, 40pin, 50pin, pinouts, матрица, ноутбук

Разъёмы 20 pin и 30 pin

| ПИН | 30 PIN 1LVDS | 30 PIN 2LVDS | 20PIN STANDART | 20PIN STANDART + EEPROM | 14PIN STANDART | 20PIN NEW STANDART вар. А А | 20PIN NEW STANDART вар. В |

| 1 | Ground | Ground | Pover suppli , 3,3V | Pover suppli , 3,3V | Pover suppli , 3,3V | Ground | Pover suppli , 3,3V |

| 2 | Pover suppli , 3,3V | Pover suppli , 3,3V | Pover suppli , 3,3V | Pover suppli , 3,3V | Pover suppli , 3,3V | Pover suppli , 3,3V | Pover suppli , 3,3V |

| 3 | Pover suppli , 3,3V | Pover suppli , 3,3V | Ground | Ground | Ground | Pover suppli , 3,3V | Ground |

| 4 | DDS 3V POVER | DDS 3V POVER | Ground | Ground | Ground | DDS 3V POVER | Ground |

| 5 | Reserved for LCD supplier test point | Reserved for LCD supplier test point | — LVDS differential data input, R0 – R5, G0 | — LVDS differential data input, R0 – R5, G0 | — LVDS differential data input, R0 – R5, G0 | Reserved for LCD supplier test point | — LVDS differential data input, R0 – R5, G0 |

| 6 | DDC Clock | DDC Clock | + LVDS differential data input, R0 – R5, G0 | + LVDS differential data input, R0 – R5, G0 | + LVDS differential data input, R0 – R5, G0 | DDC Clock | + LVDS differential data input, R0 – R5, G0 |

| 7 | DDC Data | DDC Data | Ground | Ground | — LVDS differential data input, G1 – G5, B0 – B1 | DDC Data | Ground |

| 8 | — LVDS differential data input, R0 – R5, G0 | — LVDS differential data input, R0 – R5, G0 | — LVDS differential data input, G1 – G5, B0 – B1 | — LVDS differential data input, G1 – G5, B0 – B1 | + LVDS differential data input, G1 – G5, B0 – B1 | — LVDS differential data input, R0 – R5, G0 | — LVDS differential data input, G1 – G5, B0 – B1 |

| 9 | + LVDS differential data input, R0 – R5, G0 | + LVDS differential data input, R0 – R5, G0 | + LVDS differential data input, G1 – G5, B0 – B1 | + LVDS differential data input, G1 – G5, B0 – B1 | — LVDS differential data input, B2 – B5, HS/VS/DE | + LVDS differential data input, R0 – R5, G0 | + LVDS differential data input, G1 – G5, B0 – B1 |

| 10 | Ground | Ground | Ground | Ground | + LVDS differential data input, B2 – B5, HS/VS/DE | Ground | Ground |

| 11 | — LVDS differential data input, G1 – G5, B0 – B1 | — LVDS differential data input, G1 – G5, B0 – B1 | — LVDS differential data input, B2 – B5, HS/VS/DE | — LVDS differential data input, B2 – B5, HS/VS/DE | — LVDS differential clock input | — LVDS differential data input, G1 – G5, B0 – B1 | — LVDS differential data input, B2 – B5, HS/VS/DE |

| 12 | + LVDS differential data input, G1 – G5, B0 – B1 | + LVDS differential data input, G1 – G5, B0 – B1 | + LVDS differential data input, B2 – B5, HS/VS/DE | + LVDS differential data input, B2 – B5, HS/VS/DE | +LVDS differential clock input | + LVDS differential data input, G1 – G5, B0 – B1 | + LVDS differential data input, B2 – B5, HS/VS/DE |

| 13 | Ground | Ground | Ground | Ground | Ground | Ground | Ground |

| 14 | — LVDS differential data input, B2 – B5, HS/VS/DE | — LVDS differential data input, B2 – B5, HS/VS/DE | — LVDS differential clock input | — LVDS differential clock input | Ground | — LVDS differential data input, B2 – B5, HS/VS/DE | — LVDS differential clock input |

| 15 | + LVDS differential data input, B2 – B5, HS/VS/DE | + LVDS differential data input, B2 – B5, HS/VS/DE | +LVDS differential clock input | +LVDS differential clock input | _ | + LVDS differential data input, B2 – B5, HS/VS/DE | +LVDS differential clock input |

| 16 | Ground | Ground | Ground | Ground | _ | Ground | Ground |

| 17 | — LVDS differential clock input | — LVDS differential clock input | _ | DDS 3V POVER | _ | — LVDS differential clock input | DDS 3V POVER |

| 18 | +LVDS differential clock input | +LVDS differential clock input | _ | Reserved for LCD supplier test point | _ | +LVDS differential clock input | Reserved for LCD supplier test point |

| 19 | Ground | Ground | Ground | DDC Clock | _ | Ground | DDC Clock |

| 20 | _ | — LVDS differential data input, even pixels, R0 – R5, G0 | Ground | DDC Data | _ | Ground | DDC Data |

| 21 | _ | + LVDS differential data input, even pixels, R0 – R5, G0 | _ | _ | _ | _ | _ |

| 22 | Ground | Ground | _ | _ | _ | _ | _ |

| 23 | _ | — LVDS differential data input, even pixels, G1 – G5, B0 – B1 | _ | _ | _ | _ | _ |

| 24 | _ | + LVDS differential data input, even pixels, G1 – G5, B0 – B1 | _ | _ | _ | _ | _ |

| 25 | Ground | Ground | _ | _ | _ | _ | _ |

| 26 | _ | — LVDS differential data input, even pixels, B2 – B5, HS/VS/DE | _ | _ | _ | _ | _ |

| 27 | _ | + LVDS differential data input, even pixels, B2 – B5, HS/VS/DE | _ | _ | _ | _ | _ |

| 28 | Ground | Ground | _ | _ | _ | _ | _ |

| 29 | _ | — LVDS differential clock input, even pixels | _ | _ | _ | _ | _ |

| 30 | _ | + LVDS differential clock input, even pixels | _ | _ | _ | _ | _

|

Разъём 30 pin, CCFL — подсветка, задний свет

Нажмите для увеличения изображения

Номер Пина Сигнал Описание 1 VSS Power Ground 2 VDD + 3. | Номер Пина Сигнал Описание 1 VSS Ground 2 VDD POWER SUPPLY +3.3V 3 VDD POWER SUPPLY +3.3V 4 VEEDID DDC 3.3V Power 5 NC No Connection 6 CLKEDID DDC Clock 7 DATAEDID DDC data 8 O_RxIN0- LVDS(Odd R0-R5,G0) 9 O_RxIN0+ LVDS(Odd R0-R5,G0) 10 GND Ground 11 O_RxIN1- LVDS(Odd G1-G5,B0-B1) 12 O_RxIN1+ LVDS(Odd G1-G5,B0-B1) 13 GND Ground 14 O_RxIN2- LVDS(Odd B2-B5,Sync,DE) 15 O_RxIN2+ LVDS(Odd B2-B5,Sync,DE) 16 GND Ground 17 O_RxCLK- LVDS(Odd Clock) 18 O_RxCLK+ LVDS(Odd Clock) 19 GND Ground 20 E_RxIN0- LVDS(Even R0-R5,G0 21 E_RxIN0+ LVDS(Even R0-R5,G0) 22 GND Ground 23 E_RxIN1- LVDS(Even G1-G5,B0-B1) 24 E_RxIN1+ LVDS(Even G1-G5,B0-B1) 25 GND Ground 26 E_RxIN2- LVDS(Even B2-B5,Sync,DE) 27 E_RxIN2+ LVDS(Even B2-B5,Sync,DE) 28 GND Ground 29 E_RxCLK- LVDS(Even Clock) 30 E_RxCLK+ LVDS(Even Clock) |

Распиновка 30 pin 1ch и 2ch eDP матрицы (3 и 4 контакт, дополнительный канал обычно для матриц разрешением выше 1366×768)

Нажмите для увеличения изображения

Разъём 40 pin, LED подсветка

Нажмите для увеличения изображения

Номер Пина Сигнал Описание 1 NC No Connection (Reserve) 2 AVDD PowerSupply,3.3V(typical) 3 AVDD PowerSupply,3.3V(typical) 4 DVDD DDC 3.3Vpower 5 NC No Connection (Reserve) 6 SCL DDCClock 7 SDA DDCData 8 Rin0- -LVDSdifferential data input(R0-R5,G0) 9 Rin0+ +LVDSdifferential data input(R0-R5,G0) 10 GND Ground 11 Rin1- -LVDSdifferential data input(G1-G5,B0-B1) 12 Rin1+ +LVDSdifferential data input(G1-G5,B0-B1) 13 GND Ground 14 Rin2- -LVDSdifferential data input(B2-B5,HS,VS,DE) 15 Rin2+ +LVDSdifferential data input(B2-B5,HS,VS,DE) 16 GND Ground 17 ClkIN- -LVDSdifferential clock input 18 ClkIN+ +LVDSdifferential clock input 19 GND Ground 20 NC No Connection (Reserve) 21 NC No Connection (Reserve) 22 GND Ground 23 NC No Connection (Reserve) 24 NC No Connection (Reserve) 25 GND Ground–Shield 26 NC No Connection (Reserve) 27 NC No Connection (Reserve) 28 GND Ground–Shield 29 NC No Connection (Reserve) 30 NC No Connection (Reserve) 31 VLED_GND LED Ground 32 VLED_GND LED Ground 33 VLED_GND LED Ground 34 NC No Connection (Reserve) 35 PWM System PWM Signal Input 36 LED_EN LED enable pin(+3V Input) 37 NC No Connection (Reserve) 38 VLED LED Power Supply 7V-20V 39 VLED LED Power Supply 7V-20V 40 VLED LED Power Supply 7V-20V

Номер Сигнал Описание 1 NC No Connection 2 VDD Power Supply +3.3V 3 VDD Power Supply +3.3V 4 VEDID EDID +3.3V Power 5 NC No Connect 6 CLKEDID EDID Clock Input 7 DATAEDID EDID Data Input 8 RxOIN0- -LVDS Differential Data INPUT(Odd R0-R5,G0) 9 RxOIN0+ +LVDS Differential Data INPUT(Odd R0-R5,G0) 10 VSS Ground 11 RxOIN1- -LVDS Differential Data INPUT(Odd G1-G5,B0-B1) 12 RxOIN1+ +LVDS Differential Data INPUT(Odd G1-G5,B0-B1) 13 VSS Ground 14 RxOIN2- -LVDS Differential Data INPUT(Odd B2-B5,HS,VS,DE) 15 RxOIN2+ +LVDS Differential Data INPUT(Odd B2-B5,HS,VS,DE) 16 VSS Ground 17 RxOCKIN- -LVDS Odd Differential Clock INPUT 18 RxOCKIN+ -LVDS Odd Differential Clock INPUT 19 VSS Ground 20 RxEIN0- -LVDS Differential Data INPUT(Even R0-R5,G0) 21 RxEIN0- +LVDS Differential Data INPUT(Even R0-R5,G0) 22 VSS Ground 23 RxEIN1- -LVDS Differential Data INPUT(Even G1-G5,B0-B1) 24 RxEIN1+ +LVDS Differential Data INPUT(Even G1-G5,B0-B1) 25 VSS Ground 26 RxEIN2- -LVDS Differential Data INPUT(Even B2-B5,HS,VS,DE) 27 RxEIN2+ +LVDS Differential Data INPUT(Even B2-B5,HS,VS,DE) 28 VSS Ground 29 RxECKIN- -LVDS Even Differential Clock INPUT 30 RxECKIN+ +LVDS Even Differential Clock INPUT 31 VLED_GND LED Ground 32 VLED_GND LED Ground 33 VLED_GND LED Ground 34 NC No Connection 35 S_PWMIN System PWM signal Input 36 LED_EN LED Enable Pin(+3V Input) 37 NC No Connection 38 VLED LED Power Supply 7V-21V 39 VLED LED Power Supply 7V-21V 40 VLED LED Power Supply 7V-21V

Разъём 50 pin, LED подсветка

Нажмите для увеличения изображения

Номер Пина, Сигнал, Описание 1 Test Loop (only to pin 30) Diag.pin for test 2 VEEDID (3.3v) DDC 3.3Vpower 3 VSS Ground 4 CLK EEDID DDC Clock 5 DATA EEDID DDC Data 6 VSS Ground 7 Odd_Rin0- Odd channel Differential Data Input 8 Odd_Rin0+ Odd channel Differential Data Input 9 VSS Ground 10 Odd_Rin1- Odd channel Differential Data Input 11 Odd_Rin1+ Odd channel Differential Data Input 12 VSS Ground 13 Odd_Rin2- Odd channel Differential Data Input 14 Odd_Rin2+ Odd channel Differential Data Input 15 VSS Ground 16 Odd_ClkIN- Odd channel Differential Clock Input 17 Odd_ClkIN+ Odd channel Differential Clock Input 18 VSS Ground 19 Even_Rin0- Even channel Differential Data Input 20 Even_Rin0+ Even channel Differential Data Input 21 VSS Ground 22 Even_Rin1- Even channel Differential Data Input 23 Even_Rin1+ Even channel Differential Data Input 24 VSS Ground 25 Even_Rin2- Even channel Differential Data Input 26 Even_Rin2+ Even channel Differential Data Input 27 VSS Ground 28 Even_ClkIN- Even channel Differential Clock Input 29 Even_ClkIN+ Even channel Differential Clock Input 30 Test Loop (only to pin 1) Diag.

pin for test 31 Test Loop (only to pin 50) Diag. pin for test 32 VDD Power Supply (+3.3V) 33 VDD Power Supply (+3.3V) 34 TEST (BIST_EN) BIST Function 35 +5V_ALW Power Supply (+5V) 36 VSS Ground 37 VSS Ground 38 PWM_BL Systwm side PWM input signal for brightness control 39 VBL- LED Power Ground 40 VBL- LED Power Ground 41 VBL- LED Power Ground 42 VBL- LED Power Ground 43 NC No Connection 44 VBL+ Backlight Input Voltage 45 VBL+ Backlight Input Voltage 46 VBL+ Backlight Input Voltage 47 VBL+ Backlight Input Voltage 48 SMB_DATA SMBus interface for sending brightness information 49 SMB_CLK SMBus interface for sending brightness information 50 Test Loop (only to pin 31) Diag. pin for test

Источник: optnotebook.ru

Теги этой статьи

- 20pin

- 30pin

- 40pin

- 50pin

- pinouts

- матрица

- ноутбук

- разъём

- распиновка

Близкие по теме статьи:

8 лучших ноутбуков Acer для покупки в 2018 году

879

2018, acer, год, для, дома, игр, купить

Читать

Как очистить матрицу ноутбука.

Чем и как чистить экран.

Чем и как чистить экран.

1.5 K

матрица, мочь, ноутбук, поверхность, столовый, ткань, экран

Читать

Распиновка оперативной памяти DDR4 для настольных ПК

10.3 K

ddr4, земля, контакты, общий, оперативки, памяти, питание

Читать

Распиновка разъёмов оперативной памяти ноутбука. (SIMM, SDRAM, RDRAM, DDR1, DDR2, DDR3)

7.1 K

ddr, ddr2, ddr3, dimm, microdimm, pc100, pc133

Читать

Распиновка разъёмов оперативной памяти. (SIMM, SDRAM, RDRAM, DDR1, DDR2, DDR3)

19.2 K

ddr1, ddr2, ddr3, rdram, sdram, simm, оперативная

Читать

Интересное в новостях

25/12/2022 11:38

155

Сначала у их подвала было два выхода – во второй и четвертый подъезд. Но к середине марта выходы уже были завалены, и люди пробирались в укрытие и выбирались из него через узкий лаз. Старикам и детям…

Читать полностью

01/12/2022 12:00

140

Момент бомбового удара авиации российских оккупантов по драматическому театру 16 марта 2022 г. в городе Мариуполь, Украина, унёсшего жизни нескольких сотен горожан (женщин и детей).

в городе Мариуполь, Украина, унёсшего жизни нескольких сотен горожан (женщин и детей).

Читать полностью

04/08/2022 12:50

700

Из Крыма приехали волонтёры в Мариуполь и привезли гуманитарную помощь для оставшихся в городе жителей, немного пообщались с пожилыми жителями города, мамочками с детьми и другими, кто нуждается в помощи….

Читать полностью

ReCoDa/edp-licence-compatibility-matrix-licence-descriptions.csv на мастере · dice-group/ReCoDa · GitHub

Постоянная ссылка

владелец

Тег с указанным именем ветви уже существует. Многие команды Git принимают имена как тегов, так и веток, поэтому создание этой ветки может привести к неожиданному поведению. Вы уверены, что хотите создать эту ветку?

Перейти к файлу

В настоящее время не удается получить участников

Этот файл содержит двунаправленный текст Unicode, который может быть интерпретирован или скомпилирован не так, как показано ниже. Для просмотра откройте файл в редакторе, который показывает скрытые символы Unicode.

Для просмотра откройте файл в редакторе, который показывает скрытые символы Unicode.

Подробнее о двунаправленных символах Unicode

Показать скрытые символы

| Репродукция | Распределение | Производные работы | Сублицензирование | Выдача патента | Уведомление | Атрибуция | Поделись одинаково | Копилефт | Малое авторское лево | Изменения состояния | Коммерческий | Использовать товарный знак | Ссылка | Лицензия | |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Разрешение | Разрешение | Разрешение | Разрешение | Разрешение | Требование | Требование | Требование | Требование | Требование | Требование | Запрет | Запрет | |||

| 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | https://creativecommons. org/publicdomain/zero/1.0/legalcode org/publicdomain/zero/1.0/legalcode | CC0 1.0 | |

| 1 | 1 | 1 | -1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | http://creativecommons.org/publicdomain/mark/1.0/ | CC-PDM 1.0 | |

| 1 | 1 | 0 | 0 | 0 | 1 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | http://creativecommons. org/licenses/by-nd/4.0/legalcode org/licenses/by-nd/4.0/legalcode | CC-BY-ND 4.0 | |

| 1 | 1 | 0 | 0 | 0 | 1 | 1 | 0 | 0 | 0 | 1 | 1 | 0 | http://creativecommons.org/licenses/by-nc-nd/4.0/legalcode | CC-BY-NC-ND 4.0 | |

| 1 | 1 | 1 | 0 | 0 | 1 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | http://creativecommons. org/licenses/by/4.0/legalcode org/licenses/by/4.0/legalcode | CC-BY 4.0 | |

| 1 | 1 | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | 0 | 0 | http://creativecommons.org/licenses/by-sa/4.0/legalcode | CC-BY-SA 4.0 | |

| 1 | 1 | 1 | 0 | 0 | 1 | 1 | 0 | 0 | 0 | 1 | 1 | 0 | http://creativecommons. org/licenses/by-nc/4.0/legalcode org/licenses/by-nc/4.0/legalcode | CC-BY-NC 4.0 | |

| 1 | 1 | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 0 | http://creativecommons.org/licenses/by-nc-sa/4.0/legalcode | CC-BY-NC-SA 4.0 | |

| 1 | 1 | 1 | 0 | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | https://creativecommons. org/licenses/by/3.0/at/legalcode org/licenses/by/3.0/at/legalcode | CC BY 3.0 Австрия | |

| 1 | 1 | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | http://data.norge.no/nlod/en/1.0 | НЛОД | |

| 1 | 1 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | http://data. gov.ro/base/images/logoinst/OGL-ROU-1.0.pdf gov.ro/base/images/logoinst/OGL-ROU-1.0.pdf | ОГЛ-РОУ-1.0 | |

| 1 | 1 | 1 | 0 | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | http://creativecommons.org/licenses/by/3.0/nl/legalcode | CC-BY 3.0 NL | |

| 1 | 1 | 1 | 0 | 0 | 1 | 1 | 1 | 0 | 1 | 0 | 0 | 0 | http://creativecommons. org/licenses/by-sa/3.0/nl/legalcode org/licenses/by-sa/3.0/nl/legalcode | CC-BY-SA 3.0 NL | |

| 1 | 1 | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | http://www.formez.it/iodl/ | IODL v1.0 | |

| 1 | 1 | 1 | 0 | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | http://www. dati.gov.it/iodl/2.0/ dati.gov.it/iodl/2.0/ | IODL v2.0 | |

| 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | http://opendatacommons.org/licenses/pddl/1-0/ | ОДЦ-ПДДЛ | |

| 1 | 1 | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | http://opendatacommons. org/licenses/by/1.0/ org/licenses/by/1.0/ | ОДК-BY | |

| 1 | 1 | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | http://opendatacommons.org/licenses/odbl/1.0/ | ОДЦ-ОДБЛ | |

| 1 | 1 | 1 | 1 | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | http://www. nationalarchives.gov.uk/doc/open-government-licence/version/1/ nationalarchives.gov.uk/doc/open-government-licence/version/1/ | ОГЛ 1.0 | |

| 1 | 1 | 1 | 1 | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | http://www.nationalarchives.gov.uk/doc/open-government-licence/version/2/ | Огл 2.0 | |

| 1 | 1 | 1 | 1 | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | http://www. nationalarchives.gov.uk/doc/open-government-licence/version/3/ nationalarchives.gov.uk/doc/open-government-licence/version/3/ | Огл 3.0 | |

| 1 | 1 | 1 | 1 | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | http://www.nationalarchives.gov.uk/doc/non-commercial-government-licence/non-commercial-government-licence.htm | ОГЛ-НК | |

| 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | https://www. govdata.de/dl-de/zero-2-0 govdata.de/dl-de/zero-2-0 | DL-DE-ZERO 2.0 | |

| 1 | 1 | 1 | 1 | 0 | 1 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | https://www.govdata.de/dl-de/by-2-0 | DL-DE-BY 2.0 | |

| 1 | 1 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | https://www. govdata.de/dl-de/by-1-0 govdata.de/dl-de/by-1-0 | DL-DE-BY 1.0 | |

| 1 | 1 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 1 | 0 | https://www.govdata.de/dl-de/by-nc-1-0 | DL-DE-BY-NC 1.0 | |

| 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | https://joinup. ec.europa.eu/software/page/eupl/licence-eupl ec.europa.eu/software/page/eupl/licence-eupl | EUPL-1.1 | |

| 1 | 1 | 1 | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | https://www.etalab.gouv.fr/licence-ouverte-open-licence | ФР-ЛО | |

| 1 | 0 | 0 | 0 | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | http://www. ordnancesurvey.co.uk/business-and-government/public-sector/mapping-agreements/inspire-licence.html ordnancesurvey.co.uk/business-and-government/public-sector/mapping-agreements/inspire-licence.html | ПСЕУЛ | |

| 1 | 1 | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | 0 | 0 | https://gnu.org/licenses/old-licenses/fdl-1.1 | ГФДЛ-1.1 | |

| 1 | 1 | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | 0 | 0 | https://gnu. org/licenses/old-licenses/fdl-1.2 org/licenses/old-licenses/fdl-1.2 | ГФДЛ-1.2 | |

| 1 | 1 | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | 0 | 0 | https://gnu.org/licenses/fdl-1.3.en.html | ГФДЛ-1.3 |

EDP: эффективная схема декомпозиции и сокращения для сжатия сверточной нейронной сети

. 2021 Октябрь; 32 (10): 4499-4513.

doi: 10.1109/TNNLS.2020.3018177.

Epub 2021 5 октября.

Сяофэн Руан, Юфань Лю, Чуньфэн Юань, Бин Ли, Веймин Ху, Янси Ли, Стивен Мэйбэнк

PMID:

33136545

DOI:

10.

1109/ТННЛС.2020.3018177

1109/ТННЛС.2020.3018177

Сяофэн Руань и др.

IEEE Trans Neural Netw Learn Syst.

2021 Октябрь

. 2021 Октябрь; 32 (10): 4499-4513.

doi: 10.1109/TNNLS.2020.3018177.

Epub 2021 5 октября.

Авторы

Сяофэн Руан, Юфань Лю, Чунфэн Юань, Бин Ли, Веймин Ху, Янси Ли, Стивен Мэйбэнк

PMID:

33136545

DOI:

10.1109/ТННЛС.2020.3018177

Абстрактный

В последние годы стали популярными методы сжатия моделей, которые направлены на снижение нагрузки на глубокие нейронные сети (ГНС) в реальных приложениях. Однако у большинства существующих методов сжатия есть два ограничения: 1) они обычно используют громоздкий процесс, включающий предварительное обучение, обучение с ограничением разреженности, обрезку/декомпозицию и точную настройку. Более того, последние три этапа обычно повторяются несколько раз. 2) Модели предварительно обучены при явной разреженности или предположениях низкого ранга, которые трудно гарантировать в широком смысле. В этой статье мы предлагаем эффективную схему декомпозиции и сокращения (EDP) путем создания блока с поддержкой сжатия, который может автоматически минимизировать ранг весовой матрицы и идентифицировать избыточные каналы. В частности, мы встраиваем сжатый блок, разбивая один сетевой уровень на два слоя: новый слой матрицы весов и слой матрицы коэффициентов. Путем наложения регуляризаторов на матрицу коэффициентов новая матрица весов учится становиться базисным весом низкого ранга, а соответствующие каналы становятся разреженными. Таким образом, предлагаемый сжатый блок одновременно обеспечивает низкоранговую декомпозицию и сокращение канала только за один единственный этап обучения, управляемый данными.

Однако у большинства существующих методов сжатия есть два ограничения: 1) они обычно используют громоздкий процесс, включающий предварительное обучение, обучение с ограничением разреженности, обрезку/декомпозицию и точную настройку. Более того, последние три этапа обычно повторяются несколько раз. 2) Модели предварительно обучены при явной разреженности или предположениях низкого ранга, которые трудно гарантировать в широком смысле. В этой статье мы предлагаем эффективную схему декомпозиции и сокращения (EDP) путем создания блока с поддержкой сжатия, который может автоматически минимизировать ранг весовой матрицы и идентифицировать избыточные каналы. В частности, мы встраиваем сжатый блок, разбивая один сетевой уровень на два слоя: новый слой матрицы весов и слой матрицы коэффициентов. Путем наложения регуляризаторов на матрицу коэффициентов новая матрица весов учится становиться базисным весом низкого ранга, а соответствующие каналы становятся разреженными. Таким образом, предлагаемый сжатый блок одновременно обеспечивает низкоранговую декомпозицию и сокращение канала только за один единственный этап обучения, управляемый данными. Более того, сетевая архитектура дополнительно сжимается и оптимизируется с помощью нового модуля сокращения и слияния (PM), который сокращает избыточные каналы и объединяет избыточные разложенные слои. Экспериментальные результаты (17 конкурентов) с различными наборами данных и сетями демонстрируют, что предлагаемый EDP обеспечивает высокую степень сжатия с приемлемым ухудшением точности и превосходит современные решения по степени сжатия, точности, времени вывода и оперативной памяти.

Более того, сетевая архитектура дополнительно сжимается и оптимизируется с помощью нового модуля сокращения и слияния (PM), который сокращает избыточные каналы и объединяет избыточные разложенные слои. Экспериментальные результаты (17 конкурентов) с различными наборами данных и сетями демонстрируют, что предлагаемый EDP обеспечивает высокую степень сжатия с приемлемым ухудшением точности и превосходит современные решения по степени сжатия, точности, времени вывода и оперативной памяти.

Похожие статьи

Отсечение сети с учетом дискриминации для глубокого сжатия модели.

Лю Дж., Чжуан Б., Чжуан З., Го И., Хуан Дж., Чжу Дж., Тан М.

Лю Дж. и др.

IEEE Trans Pattern Anal Mach Intell. 2022 авг; 44 (8): 4035-4051. doi: 10.1109/TPAMI.2021.3066410. Epub 2022 1 июля.

IEEE Trans Pattern Anal Mach Intell. 2022.PMID: 33755553

Слабая обрезка подсети для сильных и эффективных нейронных сетей.

Guo Q, Wu XJ, Kittler J, Feng Z.

Гуо Кью и др.

Нейронная сеть. 2021 Декабрь; 144: 614-626. doi: 10.1016/j.neunet.2021.09.015. Epub 2021 30 сентября.

Нейронная сеть. 2021.PMID: 34653719

На пути к компактным свёрточным сетям через отсечение регуляризованного фильтра с разрежённостью структуры.

Линь С, Цзи Р, Ли И, Дэн С, Ли С.

Лин С. и др.

IEEE Trans Neural Netw Learn Syst. 2020 фев; 31 (2): 574-588. дои: 10.1109/ТННЛС.2019.23. Epub 2019 12 апр.

IEEE Trans Neural Netw Learn Syst. 2020.PMID: 309

Динамическое сокращение канала путем изменения условной точности для глубоких нейронных сетей.

Chen Z, Xu TB, Du C, Liu CL, He H.

Чен Зи и др.

3V Power Supply

3 VDD + 3.3V Power Supply

4 VEDID + 3.3V EDID Power

5 AGING Aging Mode Power Supply

6 CLKEDID EDID Clock Input

7 DATAEDID EDID Data Input

8 RXIN0N -LVDS Differential Data Input

9 RXIN0P +LVDS Differential Data Input

10 VSS Power Ground

11 RXIN1N -LVDS Differential Data Input

12 RXIN1P +LVDS Differential Data Input

13 VSS Power Ground

14 RXIN2N -LVDS Differential Data Input

15 RXIN2P +LVDS Differential Data Input

16 VSS Power Ground

17 CK1INN -LVDS Differential Clock Input

18 CK1INP +LVDS Differential Clock Input

19 VSS Power Ground

20 X ---

21 X ---

22 VSS Power Ground

23 X ---

24 X ---

25 VSS Power Ground

26 X ---

27 X ---

28 VSS Power Ground

29 X ---

30 X ---

3V Power Supply

3 VDD + 3.3V Power Supply

4 VEDID + 3.3V EDID Power

5 AGING Aging Mode Power Supply

6 CLKEDID EDID Clock Input

7 DATAEDID EDID Data Input

8 RXIN0N -LVDS Differential Data Input

9 RXIN0P +LVDS Differential Data Input

10 VSS Power Ground

11 RXIN1N -LVDS Differential Data Input

12 RXIN1P +LVDS Differential Data Input

13 VSS Power Ground

14 RXIN2N -LVDS Differential Data Input

15 RXIN2P +LVDS Differential Data Input

16 VSS Power Ground

17 CK1INN -LVDS Differential Clock Input

18 CK1INP +LVDS Differential Clock Input

19 VSS Power Ground

20 X ---

21 X ---

22 VSS Power Ground

23 X ---

24 X ---

25 VSS Power Ground

26 X ---

27 X ---

28 VSS Power Ground

29 X ---

30 X ---

3V(typical)

3 AVDD PowerSupply,3.3V(typical)

4 DVDD DDC 3.3Vpower

5 NC No Connection (Reserve)

6 SCL DDCClock

7 SDA DDCData

8 Rin0- -LVDSdifferential data input(R0-R5,G0)

9 Rin0+ +LVDSdifferential data input(R0-R5,G0)

10 GND Ground

11 Rin1- -LVDSdifferential data input(G1-G5,B0-B1)

12 Rin1+ +LVDSdifferential data input(G1-G5,B0-B1)

13 GND Ground

14 Rin2- -LVDSdifferential data input(B2-B5,HS,VS,DE)

15 Rin2+ +LVDSdifferential data input(B2-B5,HS,VS,DE)

16 GND Ground

17 ClkIN- -LVDSdifferential clock input

18 ClkIN+ +LVDSdifferential clock input

19 GND Ground

20 NC No Connection (Reserve)

21 NC No Connection (Reserve)

22 GND Ground

23 NC No Connection (Reserve)

24 NC No Connection (Reserve)

25 GND Ground–Shield

26 NC No Connection (Reserve)

27 NC No Connection (Reserve)

28 GND Ground–Shield

29 NC No Connection (Reserve)

30 NC No Connection (Reserve)

31 VLED_GND LED Ground

32 VLED_GND LED Ground

33 VLED_GND LED Ground

34 NC No Connection (Reserve)

35 PWM System PWM Signal Input

36 LED_EN LED enable pin(+3V Input)

37 NC No Connection (Reserve)

38 VLED LED Power Supply 7V-20V

39 VLED LED Power Supply 7V-20V

40 VLED LED Power Supply 7V-20V

3V(typical)

3 AVDD PowerSupply,3.3V(typical)

4 DVDD DDC 3.3Vpower

5 NC No Connection (Reserve)

6 SCL DDCClock

7 SDA DDCData

8 Rin0- -LVDSdifferential data input(R0-R5,G0)

9 Rin0+ +LVDSdifferential data input(R0-R5,G0)

10 GND Ground

11 Rin1- -LVDSdifferential data input(G1-G5,B0-B1)

12 Rin1+ +LVDSdifferential data input(G1-G5,B0-B1)

13 GND Ground

14 Rin2- -LVDSdifferential data input(B2-B5,HS,VS,DE)

15 Rin2+ +LVDSdifferential data input(B2-B5,HS,VS,DE)

16 GND Ground

17 ClkIN- -LVDSdifferential clock input

18 ClkIN+ +LVDSdifferential clock input

19 GND Ground

20 NC No Connection (Reserve)

21 NC No Connection (Reserve)

22 GND Ground

23 NC No Connection (Reserve)

24 NC No Connection (Reserve)

25 GND Ground–Shield

26 NC No Connection (Reserve)

27 NC No Connection (Reserve)

28 GND Ground–Shield

29 NC No Connection (Reserve)

30 NC No Connection (Reserve)

31 VLED_GND LED Ground

32 VLED_GND LED Ground

33 VLED_GND LED Ground

34 NC No Connection (Reserve)

35 PWM System PWM Signal Input

36 LED_EN LED enable pin(+3V Input)

37 NC No Connection (Reserve)

38 VLED LED Power Supply 7V-20V

39 VLED LED Power Supply 7V-20V

40 VLED LED Power Supply 7V-20V

3V

3 VDD Power Supply +3.3V

4 VEDID EDID +3.3V Power

5 NC No Connect

6 CLKEDID EDID Clock Input

7 DATAEDID EDID Data Input

8 RxOIN0- -LVDS Differential Data INPUT(Odd R0-R5,G0)

9 RxOIN0+ +LVDS Differential Data INPUT(Odd R0-R5,G0)

10 VSS Ground

11 RxOIN1- -LVDS Differential Data INPUT(Odd G1-G5,B0-B1)

12 RxOIN1+ +LVDS Differential Data INPUT(Odd G1-G5,B0-B1)

13 VSS Ground

14 RxOIN2- -LVDS Differential Data INPUT(Odd B2-B5,HS,VS,DE)

15 RxOIN2+ +LVDS Differential Data INPUT(Odd B2-B5,HS,VS,DE)

16 VSS Ground

17 RxOCKIN- -LVDS Odd Differential Clock INPUT

18 RxOCKIN+ -LVDS Odd Differential Clock INPUT

19 VSS Ground

20 RxEIN0- -LVDS Differential Data INPUT(Even R0-R5,G0)

21 RxEIN0- +LVDS Differential Data INPUT(Even R0-R5,G0)

22 VSS Ground

23 RxEIN1- -LVDS Differential Data INPUT(Even G1-G5,B0-B1)

24 RxEIN1+ +LVDS Differential Data INPUT(Even G1-G5,B0-B1)

25 VSS Ground

26 RxEIN2- -LVDS Differential Data INPUT(Even B2-B5,HS,VS,DE)

27 RxEIN2+ +LVDS Differential Data INPUT(Even B2-B5,HS,VS,DE)

28 VSS Ground

29 RxECKIN- -LVDS Even Differential Clock INPUT

30 RxECKIN+ +LVDS Even Differential Clock INPUT

31 VLED_GND LED Ground

32 VLED_GND LED Ground

33 VLED_GND LED Ground

34 NC No Connection

35 S_PWMIN System PWM signal Input

36 LED_EN LED Enable Pin(+3V Input)

37 NC No Connection

38 VLED LED Power Supply 7V-21V

39 VLED LED Power Supply 7V-21V

40 VLED LED Power Supply 7V-21V

3V

3 VDD Power Supply +3.3V

4 VEDID EDID +3.3V Power

5 NC No Connect

6 CLKEDID EDID Clock Input

7 DATAEDID EDID Data Input

8 RxOIN0- -LVDS Differential Data INPUT(Odd R0-R5,G0)

9 RxOIN0+ +LVDS Differential Data INPUT(Odd R0-R5,G0)

10 VSS Ground

11 RxOIN1- -LVDS Differential Data INPUT(Odd G1-G5,B0-B1)

12 RxOIN1+ +LVDS Differential Data INPUT(Odd G1-G5,B0-B1)

13 VSS Ground

14 RxOIN2- -LVDS Differential Data INPUT(Odd B2-B5,HS,VS,DE)

15 RxOIN2+ +LVDS Differential Data INPUT(Odd B2-B5,HS,VS,DE)

16 VSS Ground

17 RxOCKIN- -LVDS Odd Differential Clock INPUT

18 RxOCKIN+ -LVDS Odd Differential Clock INPUT

19 VSS Ground

20 RxEIN0- -LVDS Differential Data INPUT(Even R0-R5,G0)

21 RxEIN0- +LVDS Differential Data INPUT(Even R0-R5,G0)

22 VSS Ground

23 RxEIN1- -LVDS Differential Data INPUT(Even G1-G5,B0-B1)

24 RxEIN1+ +LVDS Differential Data INPUT(Even G1-G5,B0-B1)

25 VSS Ground

26 RxEIN2- -LVDS Differential Data INPUT(Even B2-B5,HS,VS,DE)

27 RxEIN2+ +LVDS Differential Data INPUT(Even B2-B5,HS,VS,DE)

28 VSS Ground

29 RxECKIN- -LVDS Even Differential Clock INPUT

30 RxECKIN+ +LVDS Even Differential Clock INPUT

31 VLED_GND LED Ground

32 VLED_GND LED Ground

33 VLED_GND LED Ground

34 NC No Connection

35 S_PWMIN System PWM signal Input

36 LED_EN LED Enable Pin(+3V Input)

37 NC No Connection

38 VLED LED Power Supply 7V-21V

39 VLED LED Power Supply 7V-21V

40 VLED LED Power Supply 7V-21V

pin for test

2 VEEDID (3.3v) DDC 3.3Vpower

3 VSS Ground

4 CLK EEDID DDC Clock

5 DATA EEDID DDC Data

6 VSS Ground

7 Odd_Rin0- Odd channel Differential Data Input

8 Odd_Rin0+ Odd channel Differential Data Input

9 VSS Ground

10 Odd_Rin1- Odd channel Differential Data Input

11 Odd_Rin1+ Odd channel Differential Data Input

12 VSS Ground

13 Odd_Rin2- Odd channel Differential Data Input

14 Odd_Rin2+ Odd channel Differential Data Input

15 VSS Ground

16 Odd_ClkIN- Odd channel Differential Clock Input

17 Odd_ClkIN+ Odd channel Differential Clock Input

18 VSS Ground

19 Even_Rin0- Even channel Differential Data Input

20 Even_Rin0+ Even channel Differential Data Input

21 VSS Ground

22 Even_Rin1- Even channel Differential Data Input

23 Even_Rin1+ Even channel Differential Data Input

24 VSS Ground

25 Even_Rin2- Even channel Differential Data Input

26 Even_Rin2+ Even channel Differential Data Input

27 VSS Ground

28 Even_ClkIN- Even channel Differential Clock Input

29 Even_ClkIN+ Even channel Differential Clock Input

30 Test Loop (only to pin 1) Diag.

pin for test

2 VEEDID (3.3v) DDC 3.3Vpower

3 VSS Ground

4 CLK EEDID DDC Clock

5 DATA EEDID DDC Data

6 VSS Ground

7 Odd_Rin0- Odd channel Differential Data Input

8 Odd_Rin0+ Odd channel Differential Data Input

9 VSS Ground

10 Odd_Rin1- Odd channel Differential Data Input

11 Odd_Rin1+ Odd channel Differential Data Input

12 VSS Ground

13 Odd_Rin2- Odd channel Differential Data Input

14 Odd_Rin2+ Odd channel Differential Data Input

15 VSS Ground

16 Odd_ClkIN- Odd channel Differential Clock Input

17 Odd_ClkIN+ Odd channel Differential Clock Input

18 VSS Ground

19 Even_Rin0- Even channel Differential Data Input

20 Even_Rin0+ Even channel Differential Data Input

21 VSS Ground

22 Even_Rin1- Even channel Differential Data Input

23 Even_Rin1+ Even channel Differential Data Input

24 VSS Ground

25 Even_Rin2- Even channel Differential Data Input

26 Even_Rin2+ Even channel Differential Data Input

27 VSS Ground

28 Even_ClkIN- Even channel Differential Clock Input

29 Even_ClkIN+ Even channel Differential Clock Input

30 Test Loop (only to pin 1) Diag. pin for test

31 Test Loop (only to pin 50) Diag. pin for test

32 VDD Power Supply (+3.3V)

33 VDD Power Supply (+3.3V)

34 TEST (BIST_EN) BIST Function

35 +5V_ALW Power Supply (+5V)

36 VSS Ground

37 VSS Ground

38 PWM_BL Systwm side PWM input signal for brightness control

39 VBL- LED Power Ground

40 VBL- LED Power Ground

41 VBL- LED Power Ground

42 VBL- LED Power Ground

43 NC No Connection

44 VBL+ Backlight Input Voltage

45 VBL+ Backlight Input Voltage

46 VBL+ Backlight Input Voltage

47 VBL+ Backlight Input Voltage

48 SMB_DATA SMBus interface for sending brightness information

49 SMB_CLK SMBus interface for sending brightness information

50 Test Loop (only to pin 31) Diag. pin for test

pin for test

31 Test Loop (only to pin 50) Diag. pin for test

32 VDD Power Supply (+3.3V)

33 VDD Power Supply (+3.3V)

34 TEST (BIST_EN) BIST Function

35 +5V_ALW Power Supply (+5V)

36 VSS Ground

37 VSS Ground

38 PWM_BL Systwm side PWM input signal for brightness control

39 VBL- LED Power Ground

40 VBL- LED Power Ground

41 VBL- LED Power Ground

42 VBL- LED Power Ground

43 NC No Connection

44 VBL+ Backlight Input Voltage

45 VBL+ Backlight Input Voltage

46 VBL+ Backlight Input Voltage

47 VBL+ Backlight Input Voltage

48 SMB_DATA SMBus interface for sending brightness information

49 SMB_CLK SMBus interface for sending brightness information

50 Test Loop (only to pin 31) Diag. pin for test